About the Execution of LoLA for DLCround-PT-08b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 980.280 | 185404.00 | 372733.00 | 362.30 | T | normal |

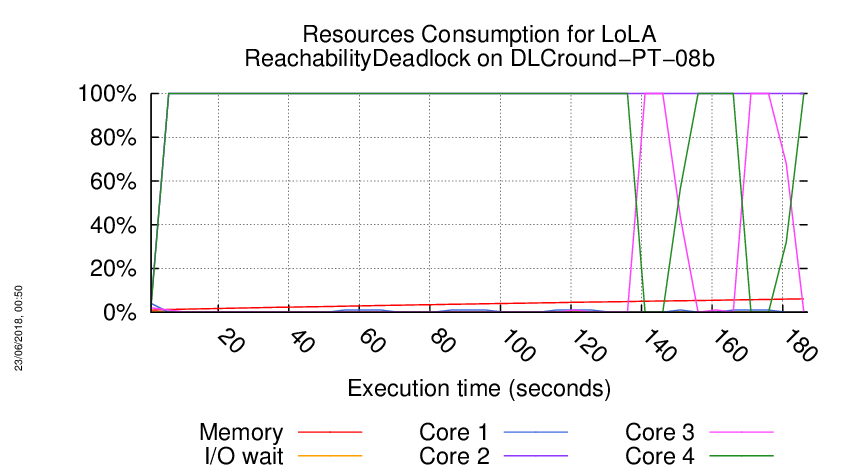

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 1.3M

-rw-r--r-- 1 mcc users 3.3K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.5K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 16K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.9K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.8K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 14K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.4K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.4K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 16K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 106 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 344 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.5K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 13K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 4 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 1.1M May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool lola

Input is DLCround-PT-08b, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r064-smll-152649735200083

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-08b-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1526630636936

info: Time: 3600 - MCC

===========================================================================================

prep: translating DLCround-PT-08b Petri net model.pnml into LoLA format

===========================================================================================

prep: translating PT Petri net complete

prep: net is already safe

prep: check for too many tokens

===========================================================================================

prep: translating DLCround-PT-08b formula ReachabilityDeadlock into LoLA format

===========================================================================================

prep: translating PT formula complete

vrfy: Checking ReachabilityDeadlock @ DLCround-PT-08b @ 3569 seconds

lola: LoLA will run for 3569 seconds at most (--timelimit)

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 7820/65536 symbol table entries, 1621 collisions

lola: preprocessing...

lola: Size of bit vector: 3088

lola: finding significant places

lola: 3088 places, 4732 transitions, 2931 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 6628 transition conflict sets

lola: TASK

lola: reading formula from DLCround-PT-08b-ReachabilityDeadlock.task

lola: E (F (DEADLOCK))

lola: rewrite Frontend/Parser/formula_rewrite.k:106

lola: checking reachability of deadlocks

lola: Planning: workflow for deadlock check: siphon||findpath||search) (--findpath=par,--siphontrap=par)

lola: STORE

lola: using a simple compression encoder (--encoder=simplecompressed)

lola: using a prefix tree store (--store=prefix)

lola: SEARCH (state space)

lola: state space: using reachability graph (--search=depth)

lola: state space: using deadlock preserving stubborn set method with insertion algorithm(--stubborn=tarjan)

lola: SEARCH (findpath)

lola: findpath: using deadlock preserving stubborn set method with insertion algorithm (--stubborn=tarjan)

lola: RUNNING

lola: findpath: starting randomized, memory-less exploration (--search=findpath)

lola: findpath: searching for paths with maximal depth 1000000 (--depthlimit)

lola: findpath: no retry limit given (--retrylimit)

lola: findpath: transitions are chosen randomly

lola: computing symmetries (--symmetry)

lola: time limit for symmetry computation of 300 seconds given (--symmtimelimit)

lola: computed 13 generators (13 in search tree, 0 by composition)

lola: representing 8192 symmetries

lola: 0 dead branches visited in search tree

lola: STP: formula with 95486 variables and 285253 clauses shipped to Minisat

lola: stp: The siphon/trap property does not hold

lola: STP completed || 1 tries, 166606 fired transitions, 0 secs || 88738 markings, 99641 edges, 17748 markings/sec, 0 secs

lola: STP completed || 1 tries, 344343 fired transitions, 5 secs || 184090 markings, 207168 edges, 19070 markings/sec, 5 secs

lola: STP completed || 1 tries, 521108 fired transitions, 10 secs || 278173 markings, 312919 edges, 18817 markings/sec, 10 secs

lola: STP completed || 1 tries, 697811 fired transitions, 15 secs || 374961 markings, 422966 edges, 19358 markings/sec, 15 secs

lola: STP completed || 1 tries, 875772 fired transitions, 20 secs || 470398 markings, 530162 edges, 19087 markings/sec, 20 secs

lola: STP completed || 2 tries, 1054275 fired transitions, 25 secs || 566003 markings, 637843 edges, 19121 markings/sec, 25 secs

lola: STP completed || 2 tries, 1232263 fired transitions, 30 secs || 661587 markings, 745457 edges, 19117 markings/sec, 30 secs

lola: STP completed || 2 tries, 1407486 fired transitions, 35 secs || 757608 markings, 853933 edges, 19204 markings/sec, 35 secs

lola: STP completed || 2 tries, 1582148 fired transitions, 40 secs || 853112 markings, 961597 edges, 19101 markings/sec, 40 secs

lola: STP completed || 2 tries, 1758651 fired transitions, 45 secs || 948861 markings, 1069884 edges, 19150 markings/sec, 45 secs

lola: STP completed || 2 tries, 1937025 fired transitions, 50 secs || 1043165 markings, 1175599 edges, 18861 markings/sec, 50 secs

lola: STP completed || 3 tries, 2113559 fired transitions, 55 secs || 1136997 markings, 1280771 edges, 18766 markings/sec, 55 secs

lola: STP completed || 3 tries, 2290450 fired transitions, 60 secs || 1232136 markings, 1388137 edges, 19028 markings/sec, 60 secs

lola: STP completed || 3 tries, 2468207 fired transitions, 65 secs || 1326988 markings, 1494940 edges, 18970 markings/sec, 65 secs

lola: STP completed || 3 tries, 2646316 fired transitions, 70 secs || 1422397 markings, 1602860 edges, 19082 markings/sec, 70 secs

lola: STP completed || 3 tries, 2825084 fired transitions, 75 secs || 1518471 markings, 1711955 edges, 19215 markings/sec, 75 secs

lola: STP completed || 4 tries, 3004096 fired transitions, 80 secs || 1613891 markings, 1819659 edges, 19084 markings/sec, 80 secs

lola: STP completed || 4 tries, 3182971 fired transitions, 85 secs || 1710038 markings, 1929091 edges, 19229 markings/sec, 85 secs

lola: STP completed || 4 tries, 3359270 fired transitions, 90 secs || 1806254 markings, 2038738 edges, 19243 markings/sec, 90 secs

lola: STP completed || 4 tries, 3538187 fired transitions, 95 secs || 1901330 markings, 2146678 edges, 19015 markings/sec, 95 secs

lola: STP completed || 4 tries, 3715901 fired transitions, 100 secs || 1997396 markings, 2256272 edges, 19213 markings/sec, 100 secs

lola: STP completed || 4 tries, 3890329 fired transitions, 105 secs || 2092729 markings, 2365012 edges, 19067 markings/sec, 105 secs

lola: STP completed || 5 tries, 4063802 fired transitions, 110 secs || 2186156 markings, 2471198 edges, 18685 markings/sec, 110 secs

lola: STP completed || 5 tries, 4237687 fired transitions, 115 secs || 2281111 markings, 2579738 edges, 18991 markings/sec, 115 secs

lola: STP completed || 5 tries, 4409296 fired transitions, 120 secs || 2374567 markings, 2686489 edges, 18691 markings/sec, 120 secs

lola: STP completed || 5 tries, 4585377 fired transitions, 125 secs || 2470225 markings, 2795995 edges, 19132 markings/sec, 125 secs

lola: STP completed || 5 tries, 4754308 fired transitions, 130 secs || 2562306 markings, 2900847 edges, 18416 markings/sec, 130 secs

lola: STP completed || 5 tries, 4925606 fired transitions, 135 secs || 2650853 markings, 3001968 edges, 17709 markings/sec, 135 secs

lola: STP completed || 6 tries, 5099147 fired transitions, 140 secs || 2743662 markings, 3107711 edges, 18562 markings/sec, 140 secs

lola: STP completed || 6 tries, 5267419 fired transitions, 145 secs || 2832861 markings, 3209724 edges, 17840 markings/sec, 145 secs

lola: STP completed || 6 tries, 5435768 fired transitions, 150 secs || 2928013 markings, 3318874 edges, 19030 markings/sec, 150 secs

lola: STP completed || 6 tries, 5607249 fired transitions, 155 secs || 3020077 markings, 3424005 edges, 18413 markings/sec, 155 secs

lola: STP completed || 6 tries, 5777878 fired transitions, 160 secs || 3112734 markings, 3529997 edges, 18531 markings/sec, 160 secs

lola: STP completed || 6 tries, 5950970 fired transitions, 165 secs || 3207915 markings, 3638989 edges, 19036 markings/sec, 165 secs

lola: STP completed || 7 tries, 6130046 fired transitions, 170 secs || 3303720 markings, 3748079 edges, 19161 markings/sec, 170 secs

lola: STP completed || 7 tries, 6308697 fired transitions, 175 secs || 3400767 markings, 3859179 edges, 19409 markings/sec, 175 secs

FORMULA DLCround-PT-08b-ReachabilityDeadlock-0 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT SAT_SMT STATE_COMPRESSION STUBBORN_SETS SYMMETRIES TOPOLOGICAL USE_NUPN UNFOLDING_TO_PT

lola: RESULT

lola: result: yes

lola: produced by: findpath

lola: The net has deadlock(s).

lola: memory consumption: 858428 KB

lola: time consumption: 185 seconds

BK_STOP 1526630822340

--------------------

content from stderr:

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-08b"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="lola"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-08b.tgz

mv DLCround-PT-08b execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool lola"

echo " Input is DLCround-PT-08b, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r064-smll-152649735200083"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;