About the Execution of Irma.struct for ClientsAndServers-PT-N0002P0

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 425.230 | 45548.00 | 4121.00 | 686.50 | T | normal |

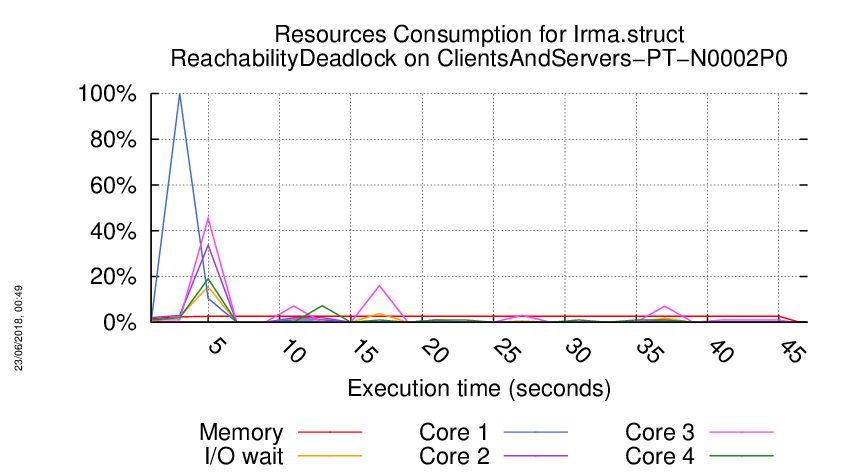

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

..............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 180K

-rw-r--r-- 1 mcc users 3.4K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 21K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:49 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.2K May 15 18:49 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.5K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 12K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.0K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.8K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.3K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 15K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 119 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 357 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 3.1K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 20K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.8K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:49 equiv_col

-rw-r--r-- 1 mcc users 8 May 15 18:49 instance

-rw-r--r-- 1 mcc users 6 May 15 18:49 iscolored

-rw-r--r-- 1 mcc users 9.1K May 15 18:49 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool irma4mcc-structural

Input is ClientsAndServers-PT-N0002P0, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r043-smll-152646359300062

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ClientsAndServers-PT-N0002P0-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1526467252958

BK_STOP 1526467298506

--------------------

content from stderr:

Prefix is 75f5f979.

Reading known information in /usr/share/mcc4mcc/75f5f979-known.json.

Reading learned information in /usr/share/mcc4mcc/75f5f979-learned.json.

Reading value translations in /usr/share/mcc4mcc/75f5f979-values.json.

Using directory /home/mcc/execution for input, as it contains a model.pnml file.

Using ClientsAndServers-PT-N0002P0 as instance name.

Using ClientsAndServers as model name.

Using algorithm or tool decision-tree.

Model characteristics are: {'Examination': 'ReachabilityDeadlock', 'Place/Transition': True, 'Colored': False, 'Relative-Time': 1, 'Relative-Memory': 1, 'Ordinary': True, 'Simple Free Choice': False, 'Extended Free Choice': False, 'State Machine': False, 'Marked Graph': False, 'Connected': True, 'Strongly Connected': True, 'Source Place': False, 'Sink Place': False, 'Source Transition': False, 'Sink Transition': False, 'Loop Free': True, 'Conservative': False, 'Sub-Conservative': False, 'Nested Units': False, 'Safe': False, 'Deadlock': None, 'Reversible': None, 'Quasi Live': True, 'Live': None}.

Known tools are: [{'Time': 401, 'Memory': 107.44, 'Tool': 'lola'}, {'Time': 5600, 'Memory': 297.95, 'Tool': 'itstools'}, {'Time': 10544, 'Memory': 197.99, 'Tool': 'gspn'}, {'Time': 18971, 'Memory': 7483.02, 'Tool': 'marcie'}].

Learned tools are: [{'Tool': 'gspn'}].

Learned tool gspn is 26.294264339152118x far from the best tool lola.

ReachabilityDeadlock lola ClientsAndServers-PT-N0002P0...

----- Start make prepare stderr -----

Time: 3600 - MCC

----- Start make prepare stdout -----

===========================================================================================

ClientsAndServers-PT-N0002P0: translating PT Petri net model.pnml into LoLA format

===========================================================================================

translating PT Petri net complete

checking for too many tokens

===========================================================================================

ClientsAndServers-PT-N0002P0: translating PT formula ReachabilityDeadlock into LoLA format

===========================================================================================

translating formula complete

touch formulae;

----- Start make result stdout -----

----- Start make result stderr -----

ReachabilityDeadlock @ ClientsAndServers-PT-N0002P0 @ 3540 seconds

----- Start make result stderr -----

----- Start make result stdout -----

lola: NET

lola: reading net from model.pnml.lola

lola: finished parsing

lola: closed net file model.pnml.lola

lola: 43/65536 symbol table entries, 0 collisions

lola: preprocessing...

lola: finding significant places

lola: 25 places, 18 transitions, 17 significant places

lola: computing forward-conflicting sets

lola: computing back-conflicting sets

lola: 25 transition conflict sets

lola: TASK

lola: reading formula from ClientsAndServers-PT-N0002P0-ReachabilityDeadlock.task

lola: E (F (DEADLOCK))

lola: E (F (DEADLOCK))

lola: checking reachability of deadlocks

lola: Planning: workflow for deadlock check: siphon||findpath||search) (--findpath=par,--siphontrap=par)

lola: STORE

lola: using a bit-perfect encoder (--encoder=bit)

lola: using 68 bytes per marking, with 0 unused bits

lola: using a prefix tree store (--store=prefix)

lola: SEARCH (state space)

lola: state space: using reachability graph (--search=depth)

lola: state space: using deadlock preserving stubborn set method with insertion algorithm(--stubborn=tarjan)

lola: SEARCH (findpath)

lola: findpath: using deadlock preserving stubborn set method with insertion algorithm (--stubborn=tarjan)

lola: RUNNING

lola: findpath: starting randomized, memory-less exploration (--search=findpath)

lola: findpath: searching for paths with maximal depth 1000000 (--depthlimit)

lola: findpath: no retry limit given (--retrylimit)

lola: findpath: transitions are chosen randomly

lola: computing symmetries (--symmetry)

lola: time limit for symmetry computation of 300 seconds given (--symmtimelimit)

lola: RESULT

lola: result: yes

lola: produced by: findpath

lola: The net has deadlock(s).

lola: computed 0 generators (0 in search tree, 0 by composition)

lola: representing 1 symmetries

lola: 0 dead branches visited in search tree

lola: STP: formula with 511 variables and 1408 clauses shipped to Minisat

lola: stp: The siphon/trap property does not hold

FORMULA ClientsAndServers-PT-N0002P0-ReachabilityDeadlock-0 TRUE TECHNIQUES COLLATERAL_PROCESSING EXPLICIT SAT_SMT STATE_COMPRESSION STUBBORN_SETS SYMMETRIES TOPOLOGICAL USE_NUPN

----- Kill lola and sara stderr -----

----- Kill lola and sara stdout -----

----- Finished stdout -----

----- Finished stderr -----

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ClientsAndServers-PT-N0002P0"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="irma4mcc-structural"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/ClientsAndServers-PT-N0002P0.tgz

mv ClientsAndServers-PT-N0002P0 execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool irma4mcc-structural"

echo " Input is ClientsAndServers-PT-N0002P0, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r043-smll-152646359300062"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;