About the Execution of ITS-Tools.L for ASLink-PT-03b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15752.830 | 128751.00 | 271813.00 | 472.70 | T | normal |

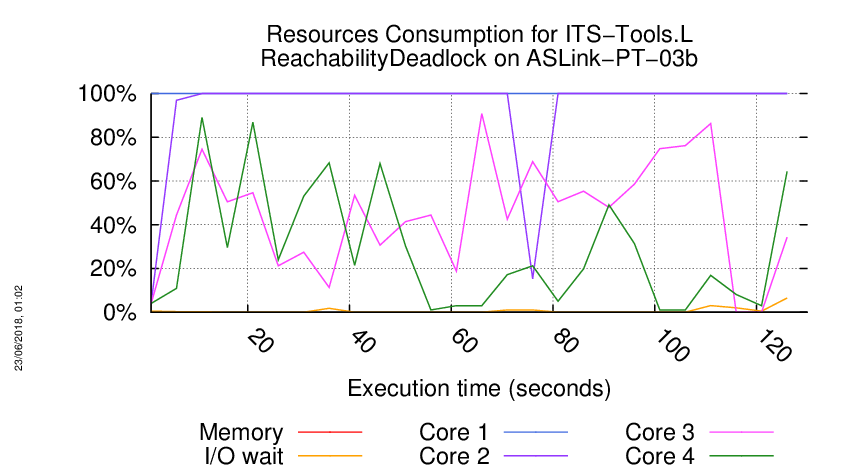

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

....................

/home/mcc/execution

total 712K

-rw-r--r-- 1 mcc users 3.7K May 29 16:53 CTLCardinality.txt

-rw-r--r-- 1 mcc users 23K May 29 16:53 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.1K May 28 11:14 CTLFireability.txt

-rw-r--r-- 1 mcc users 13K May 28 11:14 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 24 11:17 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.6K May 24 11:17 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.3K May 28 09:21 LTLCardinality.txt

-rw-r--r-- 1 mcc users 12K May 28 09:21 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 28 07:36 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.6K May 28 07:36 LTLFireability.xml

-rw-r--r-- 1 mcc users 1 May 24 11:17 NewModel

-rw-r--r-- 1 mcc users 3.4K May 27 05:07 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 17K May 27 05:07 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 104 May 26 06:29 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 342 May 26 06:29 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.6K May 26 06:34 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 15K May 26 06:34 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 28 07:31 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 28 07:31 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 24 11:17 equiv_col

-rw-r--r-- 1 mcc users 4 May 24 11:17 instance

-rw-r--r-- 1 mcc users 6 May 24 11:17 iscolored

-rw-r--r-- 1 mcc users 544K May 24 11:17 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstoolsl

Input is ASLink-PT-03b, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r273-smll-152749149500053

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME ASLink-PT-03b-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1527769312514

Flatten gal took : 495 ms

Constant places removed 1 places and 1 transitions.

Performed 736 Post agglomeration using F-continuation condition.

Iterating post reduction 0 with 737 rules applied. Total rules applied 737 place count 1637 transition count 1357

Constant places removed 781 places and 2 transitions.

Reduce isomorphic transitions removed 13 transitions.

Implicit places reduction removed 6 places :[p1367, p1239, p844, p818, p449, p423]

Performed 43 Post agglomeration using F-continuation condition.

Iterating post reduction 1 with 843 rules applied. Total rules applied 1580 place count 850 transition count 1299

Constant places removed 49 places and 0 transitions.

Performed 15 Post agglomeration using F-continuation condition.

Iterating post reduction 2 with 64 rules applied. Total rules applied 1644 place count 801 transition count 1284

Constant places removed 15 places and 0 transitions.

Implicit places reduction removed 5 places :[p1208, p1194, p813, p799, p404]

Performed 5 Post agglomeration using F-continuation condition.

Iterating post reduction 3 with 25 rules applied. Total rules applied 1669 place count 781 transition count 1279

Constant places removed 5 places and 0 transitions.

Iterating post reduction 4 with 5 rules applied. Total rules applied 1674 place count 776 transition count 1279

Performed 125 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 5 with 125 Pre rules applied. Total rules applied 1674 place count 776 transition count 1154

Constant places removed 126 places and 0 transitions.

Implicit places reduction removed 1 places :[p418]

Performed 1 Post agglomeration using F-continuation condition.

Iterating post reduction 5 with 128 rules applied. Total rules applied 1802 place count 649 transition count 1153

Constant places removed 1 places and 0 transitions.

Iterating post reduction 6 with 1 rules applied. Total rules applied 1803 place count 648 transition count 1153

Performed 1 Pre agglomeration using Quasi-Persistent + HF-interchangeable + Divergent Free condition.

Pre-agglomeration after 7 with 1 Pre rules applied. Total rules applied 1803 place count 648 transition count 1152

Constant places removed 1 places and 0 transitions.

Iterating post reduction 7 with 1 rules applied. Total rules applied 1804 place count 647 transition count 1152

Symmetric choice reduction at 8 with 14 rule applications. Total rules 1818 place count 647 transition count 1152

Constant places removed 14 places and 14 transitions.

Reduce isomorphic transitions removed 1 transitions.

Implicit places reduction removed 1 places :[p1637]

Performed 6 Post agglomeration using F-continuation condition.

Iterating post reduction 8 with 22 rules applied. Total rules applied 1840 place count 632 transition count 1131

Constant places removed 7 places and 0 transitions.

Iterating post reduction 9 with 7 rules applied. Total rules applied 1847 place count 625 transition count 1131

Symmetric choice reduction at 10 with 8 rule applications. Total rules 1855 place count 625 transition count 1131

Constant places removed 8 places and 31 transitions.

Reduce isomorphic transitions removed 1 transitions.

Implicit places reduction removed 4 places :[p1376, p1180, p785, p390]

Performed 9 Post agglomeration using F-continuation condition.

Iterating post reduction 10 with 22 rules applied. Total rules applied 1877 place count 613 transition count 1090

Constant places removed 9 places and 0 transitions.

Iterating post reduction 11 with 9 rules applied. Total rules applied 1886 place count 604 transition count 1090

Symmetric choice reduction at 12 with 4 rule applications. Total rules 1890 place count 604 transition count 1090

Constant places removed 4 places and 11 transitions.

Iterating post reduction 12 with 4 rules applied. Total rules applied 1894 place count 600 transition count 1079

Symmetric choice reduction at 13 with 1 rule applications. Total rules 1895 place count 600 transition count 1079

Constant places removed 1 places and 8 transitions.

Iterating post reduction 13 with 1 rules applied. Total rules applied 1896 place count 599 transition count 1071

Symmetric choice reduction at 14 with 1 rule applications. Total rules 1897 place count 599 transition count 1071

Constant places removed 1 places and 8 transitions.

Iterating post reduction 14 with 1 rules applied. Total rules applied 1898 place count 598 transition count 1063

Symmetric choice reduction at 15 with 1 rule applications. Total rules 1899 place count 598 transition count 1063

Constant places removed 1 places and 8 transitions.

Iterating post reduction 15 with 1 rules applied. Total rules applied 1900 place count 597 transition count 1055

Symmetric choice reduction at 16 with 1 rule applications. Total rules 1901 place count 597 transition count 1055

Constant places removed 1 places and 8 transitions.

Iterating post reduction 16 with 1 rules applied. Total rules applied 1902 place count 596 transition count 1047

Symmetric choice reduction at 17 with 1 rule applications. Total rules 1903 place count 596 transition count 1047

Constant places removed 1 places and 8 transitions.

Iterating post reduction 17 with 1 rules applied. Total rules applied 1904 place count 595 transition count 1039

Symmetric choice reduction at 18 with 1 rule applications. Total rules 1905 place count 595 transition count 1039

Constant places removed 1 places and 8 transitions.

Iterating post reduction 18 with 1 rules applied. Total rules applied 1906 place count 594 transition count 1031

Symmetric choice reduction at 19 with 1 rule applications. Total rules 1907 place count 594 transition count 1031

Constant places removed 1 places and 8 transitions.

Iterating post reduction 19 with 1 rules applied. Total rules applied 1908 place count 593 transition count 1023

Symmetric choice reduction at 20 with 1 rule applications. Total rules 1909 place count 593 transition count 1023

Constant places removed 1 places and 8 transitions.

Iterating post reduction 20 with 1 rules applied. Total rules applied 1910 place count 592 transition count 1015

Symmetric choice reduction at 21 with 1 rule applications. Total rules 1911 place count 592 transition count 1015

Constant places removed 1 places and 8 transitions.

Iterating post reduction 21 with 1 rules applied. Total rules applied 1912 place count 591 transition count 1007

Symmetric choice reduction at 22 with 1 rule applications. Total rules 1913 place count 591 transition count 1007

Constant places removed 1 places and 8 transitions.

Iterating post reduction 22 with 1 rules applied. Total rules applied 1914 place count 590 transition count 999

Symmetric choice reduction at 23 with 1 rule applications. Total rules 1915 place count 590 transition count 999

Constant places removed 1 places and 8 transitions.

Iterating post reduction 23 with 1 rules applied. Total rules applied 1916 place count 589 transition count 991

Symmetric choice reduction at 24 with 1 rule applications. Total rules 1917 place count 589 transition count 991

Constant places removed 1 places and 8 transitions.

Iterating post reduction 24 with 1 rules applied. Total rules applied 1918 place count 588 transition count 983

Symmetric choice reduction at 25 with 1 rule applications. Total rules 1919 place count 588 transition count 983

Constant places removed 1 places and 8 transitions.

Iterating post reduction 25 with 1 rules applied. Total rules applied 1920 place count 587 transition count 975

Symmetric choice reduction at 26 with 1 rule applications. Total rules 1921 place count 587 transition count 975

Constant places removed 1 places and 8 transitions.

Iterating post reduction 26 with 1 rules applied. Total rules applied 1922 place count 586 transition count 967

Symmetric choice reduction at 27 with 1 rule applications. Total rules 1923 place count 586 transition count 967

Constant places removed 1 places and 8 transitions.

Iterating post reduction 27 with 1 rules applied. Total rules applied 1924 place count 585 transition count 959

Performed 39 Post agglomeration using F-continuation condition.

Constant places removed 39 places and 0 transitions.

Iterating post reduction 28 with 39 rules applied. Total rules applied 1963 place count 546 transition count 917

Performed 1 Post agglomeration using F-continuation condition.

Constant places removed 1 places and 0 transitions.

Iterating post reduction 29 with 1 rules applied. Total rules applied 1964 place count 545 transition count 926

Applied a total of 1964 rules in 1159 ms. Remains 545 /1638 variables (removed 1093) and now considering 926/2094 (removed 1168) transitions.

// Phase 1: matrix 926 rows 545 cols

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 926 rows 545 cols

invariant :-1'p1474 + -1'p1475 + -1'p1476 + p1481 + p1482 + p1483 = 0

invariant :-1'p1528 + -1'p1529 + -1'p1530 + p1532 + p1533 + p1534 = 0

invariant :-1'p922 + -1'p925 + -1'p928 + -1'p931 + -1'p934 + -1'p937 + -1'p940 + -1'p943 + -1'p1220 + p1224 + p1227 + -1'p1232 + p1329 + -1'p1333 + p1338 + p1341 + p1344 + p1347 + p1350 + p1353 + p1356 + p1359 + p1464 + p1465 + -1'p1471 + p1475 + -1'p1482 + p1486 + -1'p1490 + p1494 + -1'p1498 + p1502 + -1'p1506 + -1'p1509 + p1513 + p1515 + p1518 + -1'p1525 + p1529 + -1'p1533 + -1'p1536 + p1540 + p1542 + p1545 + -1'p1552 + -1'p1555 + p1559 + p1561 = 0

invariant :p353 + p357 + p359 + p362 + p364 + -1'p365 + -1'p366 + -1'p367 = 0

invariant :p922 + p925 + p928 + p931 + p934 + p937 + p940 + p943 + p1213 + p1215 + p1230 + p1232 + p1233 = 1

invariant :-1'p527 + -1'p530 + -1'p533 + -1'p536 + -1'p539 + -1'p542 + -1'p545 + -1'p548 + p828 + p830 + p832 = 0

invariant :p429 + p435 + p441 + p807 = 1

invariant :p1143 + p1147 + p1149 + p1152 + p1154 + -1'p1155 + -1'p1156 + -1'p1157 = 0

invariant :p94 + p98 + p102 + p106 + p110 + p114 + p118 + p122 + p126 + -1'p221 + -1'p222 + -1'p233 + -1'p234 + -1'p238 + -1'p243 + -1'p247 + -1'p252 + -1'p294 + -1'p295 + -1'p331 + -1'p332 + -1'p365 + -1'p366 + -1'p396 + p472 + p556 + p559 + p562 + p565 + p568 + p571 + p574 + p577 = 1

invariant :p1326 + p1333 + -1'p1464 + p1471 + -1'p1475 + p1482 + -1'p1486 + p1490 + -1'p1494 + p1498 + -1'p1502 + p1506 + p1509 + p1511 + -1'p1513 + -1'p1515 + -1'p1518 + p1525 + -1'p1529 + p1533 + p1536 + p1538 + -1'p1540 + -1'p1542 + -1'p1545 + p1552 + p1555 + p1557 + -1'p1559 + -1'p1561 = 0

invariant :p1335 + -1'p1476 + -1'p1487 + -1'p1495 + -1'p1503 + -1'p1519 + -1'p1530 + -1'p1546 = 0

invariant :p551 + p609 = 1

invariant :p1323 + p1472 + p1483 + p1491 + p1499 + p1507 + p1515 + p1526 + p1534 + p1542 + p1553 + p1561 = 1

invariant :p53 + p57 + p62 + p64 + p65 + p67 + p69 + p70 + p72 + p74 + p431 + -1'p435 + -1'p441 + -1'p807 = 0

invariant :-1'p1493 + -1'p1494 + -1'p1495 + p1497 + p1498 + p1499 = 0

invariant :p1564 + p1565 + -1'p1572 + -1'p1573 + -1'p1574 = 0

invariant :p1329 + p1330 + p1336 + p1338 + p1339 + p1341 + p1342 + p1344 + p1345 + p1347 + p1348 + p1350 + p1351 + p1353 + p1354 + p1356 + p1357 + p1359 + p1360 + p1464 + p1465 + -1'p1471 + -1'p1472 + p1475 + p1476 + -1'p1482 + -1'p1483 + p1486 + p1487 + -1'p1490 + -1'p1491 + p1494 + p1495 + -1'p1498 + -1'p1499 + p1502 + p1503 + -1'p1506 + -1'p1507 + -1'p1509 + p1513 + p1518 + p1519 + -1'p1525 + -1'p1526 + p1529 + p1530 + -1'p1533 + -1'p1534 + -1'p1536 + p1540 + p1545 + p1546 + -1'p1552 + -1'p1553 + -1'p1555 + p1559 = 0

invariant :-1'p1485 + -1'p1486 + -1'p1487 + p1489 + p1490 + p1491 = 0

invariant :p49 + p53 + p57 + p62 + p69 + p70 + p72 + p74 + p431 + -1'p435 + -1'p441 + -1'p807 = 0

invariant :p227 + p230 + p232 + -1'p233 + -1'p234 + -1'p238 + -1'p239 + -1'p243 + -1'p244 + -1'p247 + -1'p248 + -1'p252 + -1'p253 + p296 + p333 + p367 + p472 = 1

invariant :p156 + p214 = 1

invariant :p622 + p625 + p627 + -1'p628 + -1'p629 + -1'p633 + -1'p634 + -1'p638 + -1'p639 + -1'p642 + -1'p643 + -1'p647 + -1'p648 + p691 + p728 + p762 + p867 = 1

invariant :-1'p1544 + -1'p1545 + -1'p1546 + p1551 + p1552 + p1553 = 0

invariant :p922 + p925 + p928 + p931 + p934 + p937 + p940 + p943 + p1020 + p1081 + p1118 + p1152 + p1213 + p1215 = 1

invariant :p1001 + p1004 + p1006 + p1011 + p1012 + p1023 + p1024 + p1028 + p1029 + p1033 + p1034 + p1037 + p1038 + p1042 + p1043 + p1084 + p1085 + p1121 + p1122 + p1155 + p1156 + p1186 + p1192 + -1'p1262 = 0

invariant :p1268 + p1386 + p1389 + p1392 + p1395 + p1574 + p1582 + p1590 + p1620 + p1628 = 1

invariant :p1220 + p1226 + p1232 + -1'p1329 + p1333 + -1'p1338 + -1'p1341 + -1'p1344 + -1'p1347 + -1'p1350 + -1'p1353 + -1'p1356 + -1'p1359 + -1'p1464 + -1'p1465 + p1471 + -1'p1475 + p1482 + -1'p1486 + p1490 + -1'p1494 + p1498 + -1'p1502 + p1506 + p1509 + -1'p1513 + -1'p1515 + -1'p1518 + p1525 + -1'p1529 + p1533 + p1536 + -1'p1540 + -1'p1542 + -1'p1545 + p1552 + p1555 + -1'p1559 + -1'p1561 = 0

invariant :p132 + p135 + p138 + p141 + p144 + p147 + p150 + p153 + p230 + p291 + p328 + p362 + p425 + p431 + -1'p435 + -1'p441 + -1'p807 = 0

invariant :p132 + p135 + p138 + p141 + p144 + p147 + p150 + p153 + p425 + p431 + -1'p435 + p439 + p443 + -1'p807 = 0

invariant :p1378 + p1386 + p1388 + p1389 + p1391 + p1392 + p1394 + p1395 + p1397 = 1

invariant :p1576 + p1577 + p1578 + -1'p1580 + -1'p1581 + -1'p1582 = 0

invariant :p9 + -1'p57 + -1'p65 + -1'p70 + -1'p74 = 0

invariant :-1'p132 + -1'p135 + -1'p138 + -1'p141 + -1'p144 + -1'p147 + -1'p150 + -1'p153 + -1'p230 + p273 + p277 + p279 + p280 + p282 + p283 + p285 + p286 + p288 + p293 + -1'p294 + -1'p295 + -1'p296 + -1'p328 + -1'p362 + -1'p425 + -1'p431 + p435 + p441 + p807 = 0

invariant :p748 + p752 + p754 + p757 + p759 + -1'p760 + -1'p761 + -1'p762 = 0

invariant :p630 + p691 + p728 + p762 + p867 = 1

invariant :-1'p1517 + -1'p1518 + -1'p1519 + p1524 + p1525 + p1526 = 0

invariant :p711 + p715 + p717 + p718 + p720 + p723 + p725 + -1'p726 + -1'p727 + -1'p728 = 0

invariant :p1509 + p1510 + p1511 + -1'p1513 + -1'p1514 + -1'p1515 = 0

invariant :p606 + p609 + p611 + p616 + p617 + p628 + p629 + p633 + p634 + p638 + p639 + p642 + p643 + p647 + p648 + p689 + p690 + p726 + p727 + p760 + p761 + p791 + p797 + -1'p867 = 0

invariant :p1602 + p1610 + -1'p1618 + -1'p1619 + -1'p1620 = 0

invariant :p1584 + p1585 + p1586 + -1'p1588 + -1'p1589 + -1'p1590 = 0

invariant :p866 + p867 = 1

invariant :p489 + p493 + p497 + p501 + p505 + p509 + p513 + p517 + p521 + -1'p616 + -1'p617 + -1'p628 + -1'p629 + -1'p633 + -1'p638 + -1'p642 + -1'p647 + -1'p689 + -1'p690 + -1'p726 + -1'p727 + -1'p760 + -1'p761 + -1'p791 + p867 + p951 + p954 + p957 + p960 + p963 + p966 + p969 + p972 = 1

invariant :p235 + p296 + p333 + p367 + p472 = 1

invariant :p492 + p496 + p500 + p504 + p508 + p512 + p516 + p520 + -1'p951 + -1'p954 + -1'p957 + -1'p960 + -1'p963 + -1'p966 + -1'p969 + -1'p972 = 0

invariant :p523 + p672 + p675 + p678 + p681 + p715 + p718 + p752 = 1

invariant :-1'p132 + -1'p135 + -1'p138 + -1'p141 + -1'p144 + -1'p147 + -1'p150 + -1'p153 + p433 + p435 + p437 = 0

invariant :-1'p527 + -1'p530 + -1'p533 + -1'p536 + -1'p539 + -1'p542 + -1'p545 + -1'p548 + -1'p625 + p668 + p672 + p674 + p675 + p677 + p678 + p680 + p681 + p683 + p688 + -1'p689 + -1'p690 + -1'p691 + -1'p723 + -1'p757 + -1'p820 + -1'p826 + p830 + p836 + p1202 = 0

invariant :p887 + p891 + p895 + p899 + p903 + p907 + p911 + p915 + p1271 + p1274 + p1277 + p1280 + p1283 + p1286 + p1289 + p1292 + p1295 + -1'p1386 + -1'p1389 + -1'p1392 + -1'p1395 + -1'p1574 + -1'p1582 + -1'p1590 + -1'p1620 + -1'p1628 = 0

invariant :p1365 + -1'p1570 + -1'p1578 + -1'p1586 + -1'p1624 = 0

invariant :p946 + p1004 = 1

invariant :-1'p922 + -1'p925 + -1'p928 + -1'p931 + -1'p934 + -1'p937 + -1'p940 + -1'p943 + -1'p1020 + p1063 + p1067 + p1069 + p1070 + p1072 + p1073 + p1075 + p1076 + p1078 + p1083 + -1'p1084 + -1'p1085 + -1'p1086 + -1'p1118 + -1'p1152 + -1'p1213 + -1'p1215 = -1

invariant :p51 + -1'p53 + -1'p57 + -1'p62 + -1'p69 + -1'p70 + -1'p72 + -1'p74 + -1'p431 + p435 + p441 + p807 = 1

invariant :-1'p887 + -1'p891 + -1'p895 + -1'p899 + -1'p903 + -1'p907 + -1'p911 + -1'p915 + p1273 + p1276 + p1279 + p1282 + p1285 + p1288 + p1291 + p1294 = 0

invariant :p10 + p14 + p18 + p22 + p26 + p30 + p34 + p38 + p42 + p57 + p65 + p70 + p74 + p161 + p164 + p167 + p170 + p173 + p176 + p179 + p182 = 1

invariant :p1017 + p1020 + p1022 + -1'p1023 + -1'p1024 + -1'p1028 + -1'p1029 + -1'p1033 + -1'p1034 + -1'p1037 + -1'p1038 + -1'p1042 + -1'p1043 + p1086 + p1123 + p1157 + p1262 = 1

invariant :p89 + p221 + p222 + p233 + p234 + p238 + p243 + p247 + p252 + p294 + p295 + p331 + p332 + p365 + p366 + p396 + -1'p472 = 0

invariant :p1536 + p1537 + p1538 + -1'p1540 + -1'p1541 + -1'p1542 = 0

invariant :p130 + p132 + p134 + p135 + p137 + p138 + p140 + p141 + p143 + p144 + p146 + p147 + p149 + p150 + p152 + p153 + p155 + -1'p277 + -1'p280 + -1'p283 + -1'p286 + -1'p320 + -1'p323 + -1'p357 = 0

invariant :p471 + p472 = 1

invariant :p1025 + p1086 + p1123 + p1157 + p1262 = 1

invariant :p1202 + p1204 + p1206 + p1213 = 1

invariant :p879 + p1011 + p1012 + p1023 + p1024 + p1028 + p1033 + p1037 + p1042 + p1084 + p1085 + p1121 + p1122 + p1155 + p1156 + p1186 + -1'p1262 = 0

invariant :p918 + p1067 + p1070 + p1073 + p1076 + p1110 + p1113 + p1147 = 1

invariant :p1261 + p1262 = 1

invariant :p128 + p277 + p280 + p283 + p286 + p320 + p323 + p357 = 1

invariant :p1568 + p1569 + p1570 + -1'p1572 + -1'p1573 + -1'p1574 = 0

invariant :-1'p1501 + -1'p1502 + -1'p1503 + p1505 + p1506 + p1507 = 0

invariant :p97 + p101 + p105 + p109 + p113 + p117 + p121 + p125 + -1'p556 + -1'p559 + -1'p562 + -1'p565 + -1'p568 + -1'p571 + -1'p574 + -1'p577 = 0

invariant :p920 + p922 + p924 + p925 + p927 + p928 + p930 + p931 + p933 + p934 + p936 + p937 + p939 + p940 + p942 + p943 + p945 + -1'p1067 + -1'p1070 + -1'p1073 + -1'p1076 + -1'p1110 + -1'p1113 + -1'p1147 = 0

invariant :p13 + p17 + p21 + p25 + p29 + p33 + p37 + p41 + -1'p161 + -1'p164 + -1'p167 + -1'p170 + -1'p173 + -1'p176 + -1'p179 + -1'p182 = 0

invariant :-1'p1463 + -1'p1464 + -1'p1465 + p1470 + p1471 + p1472 = 0

invariant :p824 + p830 + p836 + p1202 = 1

invariant :p884 + p887 + p888 + p891 + p892 + p895 + p896 + p899 + p900 + p903 + p904 + p907 + p908 + p911 + p912 + p915 + p916 + -1'p1011 + -1'p1012 + -1'p1023 + -1'p1024 + -1'p1028 + -1'p1033 + -1'p1037 + -1'p1042 + -1'p1084 + -1'p1085 + -1'p1121 + -1'p1122 + -1'p1155 + -1'p1156 + -1'p1186 + p1262 = 1

invariant :p1106 + p1110 + p1112 + p1113 + p1115 + p1118 + p1120 + -1'p1121 + -1'p1122 + -1'p1123 = 0

invariant :p316 + p320 + p322 + p323 + p325 + p328 + p330 + -1'p331 + -1'p332 + -1'p333 = 0

invariant :p807 + p809 + p811 + p826 + -1'p830 + -1'p836 + -1'p1202 = 0

invariant :p412 + p431 + -1'p435 + -1'p441 + -1'p807 = 0

invariant :-1'p1213 + p1218 + p1220 + p1221 = 0

invariant :p1622 + p1623 + p1624 + -1'p1626 + -1'p1627 + -1'p1628 = 0

invariant :p1328 + -1'p1465 + -1'p1511 + -1'p1538 + -1'p1557 = 0

invariant :p484 + p616 + p617 + p628 + p629 + p633 + p638 + p642 + p647 + p689 + p690 + p726 + p727 + p760 + p761 + p791 + -1'p867 = 0

invariant :p554 + p556 + p557 + p559 + p560 + p562 + p563 + p565 + p566 + p568 + p569 + p571 + p572 + p574 + p575 + p577 + p578 + -1'p609 = 0

invariant :p1369 + p1570 + p1578 + p1586 + p1624 = 1

invariant :p159 + p161 + p162 + p164 + p165 + p167 + p168 + p170 + p171 + p173 + p174 + p176 + p177 + p179 + p180 + p182 + p183 + -1'p214 = 0

invariant :p1386 + p1388 + p1389 + p1391 + p1392 + p1394 + p1395 + p1397 + p1398 + p1459 + p1463 + p1464 + p1465 + p1474 + p1475 + p1476 + p1485 + p1486 + p1487 + p1493 + p1494 + p1495 + p1501 + p1502 + p1503 + p1513 + p1514 + p1515 + p1517 + p1518 + p1519 + p1528 + p1529 + p1530 + p1540 + p1541 + p1542 + p1544 + p1545 + p1546 + p1559 + p1560 + p1561 + p1572 + p1573 + p1574 + p1580 + p1581 + p1582 + p1588 + p1589 + p1590 + p1618 + p1619 + p1620 + p1626 + p1627 + p1628 = 1

invariant :p1555 + p1556 + p1557 + -1'p1559 + -1'p1560 + -1'p1561 = 0

invariant :p527 + p530 + p533 + p536 + p539 + p542 + p545 + p548 + p625 + p686 + p723 + p757 + p820 + p826 + -1'p830 + -1'p836 + -1'p1202 = 0

invariant :p525 + p527 + p529 + p530 + p532 + p533 + p535 + p536 + p538 + p539 + p541 + p542 + p544 + p545 + p547 + p548 + p550 + -1'p672 + -1'p675 + -1'p678 + -1'p681 + -1'p715 + -1'p718 + -1'p752 = 0

invariant :p211 + p214 + p216 + p221 + p222 + p233 + p234 + p238 + p239 + p243 + p244 + p247 + p248 + p252 + p253 + p294 + p295 + p331 + p332 + p365 + p366 + p396 + p402 + -1'p472 = 0

invariant :p949 + p951 + p952 + p954 + p955 + p957 + p958 + p960 + p961 + p963 + p964 + p966 + p967 + p969 + p970 + p972 + p973 + -1'p1004 = 0

invariant :p527 + p530 + p533 + p536 + p539 + p542 + p545 + p548 + p820 + p826 + -1'p830 + p834 + p838 + -1'p1202 = 0

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ctl-linux64, --gc-threshold, 2000000, --quiet, -i, /home/mcc/execution/ReachabilityDeadlock.pnml.gal, -t, CGAL, -ctl, DEADLOCK], workingDir=/home/mcc/execution]

its-ctl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805241334/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/ReachabilityDeadlock.pnml.gal -t CGAL -ctl DEADLOCK

No direction supplied, using forward translation only.

built 3 ordering constraints for composite.

built 811 ordering constraints for composite.

built 554 ordering constraints for composite.

built 346 ordering constraints for composite.

built 140 ordering constraints for composite.

built 138 ordering constraints for composite.

built 336 ordering constraints for composite.

built 336 ordering constraints for composite.

built 342 ordering constraints for composite.

built 342 ordering constraints for composite.

built 391 ordering constraints for composite.

built 391 ordering constraints for composite.

built 293 ordering constraints for composite.

built 266 ordering constraints for composite.

built 264 ordering constraints for composite.

built 255 ordering constraints for composite.

built 111 ordering constraints for composite.

built 5 ordering constraints for composite.

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O3, model.c], workingDir=/home/mcc/execution]

Compilation finished in 15015 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 159 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, -d], workingDir=/home/mcc/execution]

LTSmin run took 3108 ms.

FORMULA ASLink-PT-03b-ReachabilityDeadlock-0 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

ITS tools runner thread asked to quit. Dying gracefully.

BK_STOP 1527769441265

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution ReachabilityDeadlock -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination ReachabilityDeadlock -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -louvain -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

May 31, 2018 12:21:54 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, ReachabilityDeadlock, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -louvain, -smt]

May 31, 2018 12:21:54 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

May 31, 2018 12:21:54 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 225 ms

May 31, 2018 12:21:54 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 1638 places.

May 31, 2018 12:21:55 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 2094 transitions.

May 31, 2018 12:21:55 PM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

May 31, 2018 12:21:55 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 56 ms

May 31, 2018 12:21:55 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 490 ms

May 31, 2018 12:21:55 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.simple.gal : 17 ms

May 31, 2018 12:21:55 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 2094 transitions.

May 31, 2018 12:21:57 PM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

May 31, 2018 12:21:58 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 926 transitions.

May 31, 2018 12:21:58 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 162 ms

May 31, 2018 12:21:58 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 141 ms

May 31, 2018 12:21:58 PM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

May 31, 2018 12:21:58 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 139 ms

May 31, 2018 12:21:58 PM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

May 31, 2018 12:21:58 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 92 place invariants in 293 ms

May 31, 2018 12:22:00 PM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 1276 redundant transitions.

May 31, 2018 12:22:00 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/ReachabilityDeadlock.pnml.gal : 33 ms

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 545 variables to be positive in 2986 ms

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 926 transitions.

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/926 took 1 ms. Total solver calls (SAT/UNSAT): 0(0/0)

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 154 ms. Total solver calls (SAT/UNSAT): 0(0/0)

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 926 transitions.

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 61 ms. Total solver calls (SAT/UNSAT): 0(0/0)

May 31, 2018 12:22:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 926 transitions.

May 31, 2018 12:22:04 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(8/926) took 3135 ms. Total solver calls (SAT/UNSAT): 1274(1211/63)

May 31, 2018 12:22:07 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(32/926) took 6154 ms. Total solver calls (SAT/UNSAT): 4454(4391/63)

May 31, 2018 12:22:10 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(62/926) took 9195 ms. Total solver calls (SAT/UNSAT): 7619(7556/63)

May 31, 2018 12:22:13 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(100/926) took 12226 ms. Total solver calls (SAT/UNSAT): 11986(8208/3778)

May 31, 2018 12:22:17 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(142/926) took 15297 ms. Total solver calls (SAT/UNSAT): 16267(9868/6399)

May 31, 2018 12:22:20 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(169/926) took 18372 ms. Total solver calls (SAT/UNSAT): 19642(13243/6399)

May 31, 2018 12:22:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(200/926) took 21472 ms. Total solver calls (SAT/UNSAT): 22708(16271/6437)

May 31, 2018 12:22:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(224/926) took 24517 ms. Total solver calls (SAT/UNSAT): 25027(18286/6741)

May 31, 2018 12:22:29 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(246/926) took 27598 ms. Total solver calls (SAT/UNSAT): 28206(21465/6741)

May 31, 2018 12:22:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(271/926) took 30614 ms. Total solver calls (SAT/UNSAT): 31231(24490/6741)

May 31, 2018 12:22:35 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(304/926) took 33714 ms. Total solver calls (SAT/UNSAT): 33864(26677/7187)

May 31, 2018 12:22:38 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(334/926) took 36978 ms. Total solver calls (SAT/UNSAT): 35332(27793/7539)

May 31, 2018 12:22:41 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(363/926) took 39979 ms. Total solver calls (SAT/UNSAT): 36745(28605/8140)

May 31, 2018 12:22:45 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(391/926) took 43479 ms. Total solver calls (SAT/UNSAT): 38470(29363/9107)

May 31, 2018 12:22:51 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(398/926) took 49330 ms. Total solver calls (SAT/UNSAT): 39091(29525/9566)

May 31, 2018 12:22:54 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(402/926) took 52973 ms. Total solver calls (SAT/UNSAT): 39457(29673/9784)

May 31, 2018 12:22:58 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(407/926) took 56670 ms. Total solver calls (SAT/UNSAT): 39860(29923/9937)

May 31, 2018 12:23:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(423/926) took 59894 ms. Total solver calls (SAT/UNSAT): 40733(30367/10366)

May 31, 2018 12:23:04 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(436/926) took 62975 ms. Total solver calls (SAT/UNSAT): 41660(30945/10715)

May 31, 2018 12:23:07 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(505/926) took 66218 ms. Total solver calls (SAT/UNSAT): 44393(31342/13051)

May 31, 2018 12:23:10 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(566/926) took 69233 ms. Total solver calls (SAT/UNSAT): 46659(33608/13051)

May 31, 2018 12:23:14 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(607/926) took 72270 ms. Total solver calls (SAT/UNSAT): 48601(35550/13051)

May 31, 2018 12:23:17 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(663/926) took 75273 ms. Total solver calls (SAT/UNSAT): 50771(37656/13115)

May 31, 2018 12:23:20 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(712/926) took 78558 ms. Total solver calls (SAT/UNSAT): 52446(39246/13200)

May 31, 2018 12:23:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(739/926) took 81611 ms. Total solver calls (SAT/UNSAT): 53854(40283/13571)

May 31, 2018 12:23:26 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(846/926) took 84655 ms. Total solver calls (SAT/UNSAT): 55079(41080/13999)

May 31, 2018 12:23:29 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(914/926) took 87687 ms. Total solver calls (SAT/UNSAT): 56322(41459/14863)

May 31, 2018 12:23:30 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 88286 ms. Total solver calls (SAT/UNSAT): 56377(41506/14871)

May 31, 2018 12:23:30 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 926 transitions.

May 31, 2018 12:23:41 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Completed DNA matrix. took 11581 ms. Total solver calls (SAT/UNSAT): 6991(0/6991)

May 31, 2018 12:23:41 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 103948ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="ASLink-PT-03b"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="itstoolsl"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/ASLink-PT-03b.tgz

mv ASLink-PT-03b execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstoolsl"

echo " Input is ASLink-PT-03b, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r273-smll-152749149500053"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;