About the Execution of ITS-Tools for FlexibleBarrier-PT-08b

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15754.750 | 641170.00 | 1188788.00 | 235.90 | FT?TFFF????????? | normal |

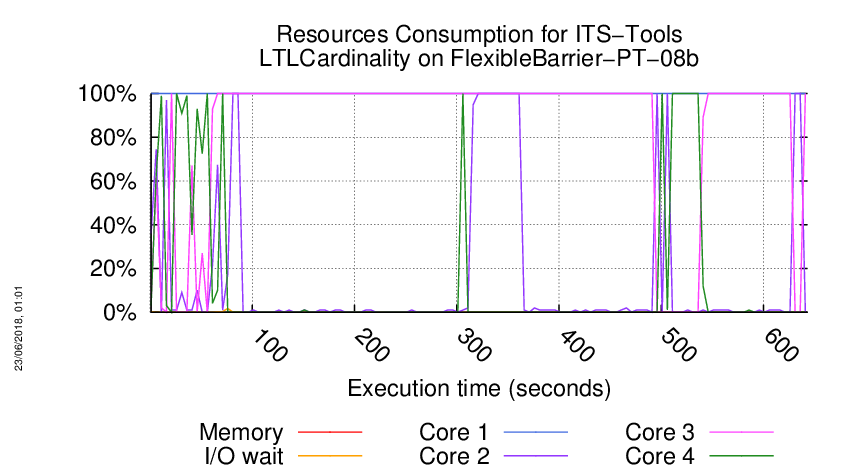

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

.................................

/home/mcc/execution

total 404K

-rw-r--r-- 1 mcc users 3.5K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.3K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 13K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.1K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.7K May 26 09:26 LTLCardinality.txt

-rw-r--r-- 1 mcc users 13K May 26 09:26 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.9K May 26 09:26 LTLFireability.txt

-rw-r--r-- 1 mcc users 9.1K May 26 09:26 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.3K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 16K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 113 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 351 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.7K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 16K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 4 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 241K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstools

Input is FlexibleBarrier-PT-08b, examination is LTLCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r248-blw7-152732549700039

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-00

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-01

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-02

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-03

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-04

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-05

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-06

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-07

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-08

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-09

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-10

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-11

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-12

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-13

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-14

FORMULA_NAME FlexibleBarrier-PT-08b-LTLCardinality-15

=== Now, execution of the tool begins

BK_START 1527960627870

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ltl-linux64, --gc-threshold, 2000000, -i, /home/mcc/execution/LTLCardinality.pnml.gal, -t, CGAL, -LTL, /home/mcc/execution/LTLCardinality.ltl, -c, -stutter-deadlock], workingDir=/home/mcc/execution]

its-ltl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ltl-linux64 --gc-threshold 2000000 -i /home/mcc/execution/LTLCardinality.pnml.gal -t CGAL -LTL /home/mcc/execution/LTLCardinality.ltl -c -stutter-deadlock

Read 16 LTL properties

Checking formula 0 : !(((F(G("(u17.p804>=3)")))U(("((u17.p718==0)||(u12.p381==1))")U("(u11.p296>=1)"))))

Formula 0 simplified : !(FG"(u17.p804>=3)" U ("((u17.p718==0)||(u12.p381==1))" U "(u11.p296>=1)"))

built 53 ordering constraints for composite.

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

// Phase 1: matrix 1057 rows 920 cols

invariant :u9:p92 + u9:p93 + u9:p94 + u9:p95 + u9:p96 + u9:p97 + u9:p98 + u9:p99 + u9:p100 + u9:p101 + u9:p102 + u9:p103 + u9:p104 + u9:p105 + u9:p106 + u9:p107 + u9:p108 + u9:p109 + u9:p110 + u9:p111 + u9:p112 + u9:p113 + u9:p114 + u9:p115 + u9:p116 + u9:p117 + u9:p118 + u9:p119 + u9:p120 + u9:p121 + u9:p122 + u9:p123 + u9:p124 + u9:p125 + u9:p126 + u9:p127 + u9:p128 + u9:p129 + u9:p130 + u9:p131 + u9:p132 + u9:p133 + u9:p134 + u9:p135 + u9:p136 + u9:p137 + u9:p138 + u9:p139 + u9:p140 + u9:p141 + u9:p142 + u9:p143 + u9:p144 + u9:p145 + u9:p146 + u9:p147 + u9:p148 + u9:p149 + u9:p150 + u9:p151 + u9:p152 + u9:p153 + u9:p154 + u9:p155 + u9:p156 + u9:p157 + u9:p158 + u9:p159 + u9:p160 + u9:p161 + u9:p162 + u9:p163 + u9:p164 + u9:p165 + u9:p166 + u9:p167 + u9:p168 + u9:p169 + u9:p170 + u9:p171 + u9:p172 + u9:p173 + u9:p174 + u9:p175 + u21:p7 + u20:p6 + u19:p5 + u27:p4 + u26:p3 + u25:p2 + u24:p1 + u22:p0 = 1

invariant :u15:p596 + u15:p597 + u15:p598 + u15:p599 + u15:p600 + u15:p601 + u15:p602 + u15:p603 + u15:p604 + u15:p605 + u15:p606 + u15:p607 + u15:p608 + u15:p609 + u15:p610 + u15:p611 + u15:p612 + u15:p613 + u15:p614 + u15:p615 + u15:p616 + u15:p617 + u15:p618 + u15:p619 + u15:p620 + u15:p621 + u15:p622 + u15:p623 + u15:p624 + u15:p625 + u15:p626 + u15:p627 + u15:p628 + u15:p629 + u15:p630 + u15:p631 + u15:p632 + u15:p633 + u15:p634 + u15:p635 + u15:p636 + u15:p637 + u15:p638 + u15:p639 + u15:p640 + u15:p641 + u15:p642 + u15:p643 + u15:p644 + u15:p645 + u15:p646 + u15:p647 + u15:p648 + u15:p649 + u15:p650 + u15:p651 + u15:p652 + u15:p653 + u15:p654 + u24:p1 + u22:p0 = 1

invariant :u10:p176 + u10:p177 + u10:p178 + u10:p179 + u10:p180 + u10:p181 + u10:p182 + u10:p183 + u10:p184 + u10:p185 + u10:p186 + u10:p187 + u10:p188 + u10:p189 + u10:p190 + u10:p191 + u10:p192 + u10:p193 + u10:p194 + u10:p195 + u10:p196 + u10:p197 + u10:p198 + u10:p199 + u10:p200 + u10:p201 + u10:p202 + u10:p203 + u10:p204 + u10:p205 + u10:p206 + u10:p207 + u10:p208 + u10:p209 + u10:p210 + u10:p211 + u10:p212 + u10:p213 + u10:p214 + u10:p215 + u10:p216 + u10:p217 + u10:p218 + u10:p219 + u10:p220 + u10:p221 + u10:p222 + u10:p223 + u10:p224 + u10:p225 + u10:p226 + u10:p227 + u10:p228 + u10:p229 + u10:p230 + u10:p231 + u10:p232 + u10:p233 + u10:p234 + u10:p235 + u10:p236 + u10:p237 + u10:p238 + u10:p239 + u10:p240 + u10:p241 + u10:p242 + u10:p243 + u10:p244 + u10:p245 + u10:p246 + u10:p247 + u10:p248 + u10:p249 + u10:p250 + u10:p251 + u10:p252 + u10:p253 + u10:p254 + u10:p255 + u10:p256 + u10:p257 + u10:p258 + u10:p259 + u20:p6 + u19:p5 + u27:p4 + u26:p3 + u25:p2 + u24:p1 + u22:p0 = 1

invariant :u8:p8 + u8:p9 + u8:p10 + u8:p11 + u8:p12 + u8:p13 + u8:p14 + u8:p15 + u8:p16 + u8:p17 + u8:p18 + u8:p19 + u8:p20 + u8:p21 + u8:p22 + u8:p23 + u8:p24 + u8:p25 + u8:p26 + u8:p27 + u8:p28 + u8:p29 + u8:p30 + u8:p31 + u8:p32 + u8:p33 + u8:p34 + u8:p35 + u8:p36 + u8:p37 + u8:p38 + u8:p39 + u8:p40 + u8:p41 + u8:p42 + u8:p43 + u8:p44 + u8:p45 + u8:p46 + u8:p47 + u8:p48 + u8:p49 + u8:p50 + u8:p51 + u8:p52 + u8:p53 + u8:p54 + u8:p55 + u8:p56 + u8:p57 + u8:p58 + u8:p59 + u8:p60 + u8:p61 + u8:p62 + u8:p63 + u8:p64 + u8:p65 + u8:p66 + u8:p67 + u8:p68 + u8:p69 + u8:p70 + u8:p71 + u8:p72 + u8:p73 + u8:p74 + u8:p75 + u8:p76 + u8:p77 + u8:p78 + u8:p79 + u8:p80 + u8:p81 + u8:p82 + u8:p83 + u8:p84 + u8:p85 + u8:p86 + u8:p87 + u8:p88 + u8:p89 + u8:p90 + u8:p91 + u21:p7 + u20:p6 + u19:p5 + u27:p4 + u26:p3 + u25:p2 + u24:p1 + u22:p0 = 1

invariant :u14:p512 + u14:p513 + u14:p514 + u14:p515 + u14:p516 + u14:p517 + u14:p518 + u14:p519 + u14:p520 + u14:p521 + u14:p522 + u14:p523 + u14:p524 + u14:p525 + u14:p526 + u14:p527 + u14:p528 + u14:p529 + u14:p530 + u14:p531 + u14:p532 + u14:p533 + u14:p534 + u14:p535 + u14:p536 + u14:p537 + u14:p538 + u14:p539 + u14:p540 + u14:p541 + u14:p542 + u14:p543 + u14:p544 + u14:p545 + u14:p546 + u14:p547 + u14:p548 + u14:p549 + u14:p550 + u14:p551 + u14:p552 + u14:p553 + u14:p554 + u14:p555 + u14:p556 + u14:p557 + u14:p558 + u14:p559 + u14:p560 + u14:p561 + u14:p562 + u14:p563 + u14:p564 + u14:p565 + u14:p566 + u14:p567 + u14:p568 + u14:p569 + u14:p570 + u14:p571 + u14:p572 + u14:p573 + u14:p574 + u14:p575 + u14:p576 + u14:p577 + u14:p578 + u14:p579 + u14:p580 + u14:p581 + u14:p582 + u14:p583 + u14:p584 + u14:p585 + u14:p586 + u14:p587 + u14:p588 + u14:p589 + u14:p590 + u14:p591 + u14:p592 + u14:p593 + u14:p594 + u14:p595 + u25:p2 + u24:p1 + u22:p0 = 1

invariant :u18:p908 + u18:p909 + u18:p910 + u18:p911 + u18:p912 + u18:p913 + u18:p914 + u18:p915 + u18:p916 + u18:p917 + u18:p918 + u18:p919 + u23:p655 + u22:p0 = 1

invariant :u17:p656 + u17:p657 + u17:p658 + u17:p659 + u17:p660 + u17:p661 + u17:p662 + u17:p663 + u17:p664 + u17:p665 + u17:p666 + u17:p667 + u17:p668 + u17:p669 + u17:p670 + u17:p671 + u17:p672 + u17:p673 + u17:p674 + u17:p675 + u17:p676 + u17:p677 + u17:p678 + u17:p679 + u17:p680 + u17:p681 + u17:p682 + u17:p683 + u17:p684 + u17:p685 + u17:p686 + u17:p687 + u17:p688 + u17:p689 + u17:p690 + u17:p691 + u17:p692 + u17:p693 + u17:p694 + u17:p695 + u17:p696 + u17:p697 + u17:p698 + u17:p699 + u17:p700 + u17:p701 + u17:p702 + u17:p703 + u17:p704 + u17:p705 + u17:p706 + u17:p707 + u17:p708 + u17:p709 + u17:p710 + u17:p711 + u17:p712 + u17:p713 + u17:p714 + u17:p715 + u17:p716 + u17:p717 + u17:p718 + u17:p719 + u17:p720 + u17:p721 + u17:p722 + u17:p723 + u17:p724 + u17:p725 + u17:p726 + u17:p727 + u17:p728 + u17:p729 + u17:p730 + u17:p731 + u17:p732 + u17:p733 + u17:p734 + u17:p735 + u17:p736 + u17:p737 + u17:p738 + u17:p739 + u17:p740 + u17:p741 + u17:p742 + u17:p743 + u17:p744 + u17:p745 + u17:p746 + u17:p747 + u17:p748 + u17:p749 + u17:p750 + u17:p751 + u17:p752 + u17:p753 + u17:p754 + u17:p755 + u17:p756 + u17:p757 + u17:p758 + u17:p759 + u17:p760 + u17:p761 + u17:p762 + u17:p763 + u17:p764 + u17:p765 + u17:p766 + u17:p767 + u17:p768 + u17:p769 + u17:p770 + u17:p771 + u17:p772 + u17:p773 + u17:p774 + u17:p775 + u17:p776 + u17:p777 + u17:p778 + u17:p779 + u17:p780 + u17:p781 + u17:p782 + u17:p783 + u17:p784 + u17:p785 + u17:p786 + u17:p787 + u17:p788 + u17:p789 + u17:p790 + u17:p791 + u17:p792 + u17:p793 + u17:p794 + u17:p795 + u17:p796 + u17:p797 + u17:p798 + u17:p799 + u17:p800 + u17:p801 + u17:p802 + u17:p803 + u17:p804 + u17:p805 + u17:p806 + u17:p807 + u17:p808 + u17:p809 + u17:p810 + u17:p811 + u17:p812 + u17:p813 + u17:p814 + u17:p815 + u17:p816 + u17:p817 + u17:p818 + u17:p819 + u17:p820 + u17:p821 + u17:p822 + u17:p823 + u17:p824 + u17:p825 + u17:p826 + u17:p827 + u17:p828 + u17:p829 + u17:p830 + u17:p831 + u17:p832 + u17:p833 + u17:p834 + u17:p835 + u17:p836 + u17:p837 + u17:p838 + u17:p839 + u17:p840 + u17:p841 + u17:p842 + u17:p843 + u17:p844 + u17:p845 + u17:p846 + u17:p847 + u17:p848 + u17:p849 + u17:p850 + u17:p851 + u17:p852 + u17:p853 + u17:p854 + u17:p855 + u17:p856 + u17:p857 + u17:p858 + u17:p859 + u17:p860 + u17:p861 + u17:p862 + u17:p863 + u17:p864 + u17:p865 + u17:p866 + u17:p867 + u17:p868 + u17:p869 + u17:p870 + u17:p871 + u17:p872 + u17:p873 + u17:p874 + u17:p875 + u17:p876 + u17:p877 + u17:p878 + u17:p879 + u17:p880 + u17:p881 + u17:p882 + u17:p883 + u17:p884 + u17:p885 + u17:p886 + u17:p887 + u17:p888 + u17:p889 + u17:p890 + u17:p891 + u17:p892 + u17:p893 + u17:p894 + u17:p895 + u17:p896 + u17:p897 + u17:p898 + u17:p899 + u17:p900 + u17:p901 + u17:p902 + u17:p903 + u17:p904 + u17:p905 + u17:p906 + u17:p907 + u23:p655 + u22:p0 = 1

invariant :u13:p428 + u13:p429 + u13:p430 + u13:p431 + u13:p432 + u13:p433 + u13:p434 + u13:p435 + u13:p436 + u13:p437 + u13:p438 + u13:p439 + u13:p440 + u13:p441 + u13:p442 + u13:p443 + u13:p444 + u13:p445 + u13:p446 + u13:p447 + u13:p448 + u13:p449 + u13:p450 + u13:p451 + u13:p452 + u13:p453 + u13:p454 + u13:p455 + u13:p456 + u13:p457 + u13:p458 + u13:p459 + u13:p460 + u13:p461 + u13:p462 + u13:p463 + u13:p464 + u13:p465 + u13:p466 + u13:p467 + u13:p468 + u13:p469 + u13:p470 + u13:p471 + u13:p472 + u13:p473 + u13:p474 + u13:p475 + u13:p476 + u13:p477 + u13:p478 + u13:p479 + u13:p480 + u13:p481 + u13:p482 + u13:p483 + u13:p484 + u13:p485 + u13:p486 + u13:p487 + u13:p488 + u13:p489 + u13:p490 + u13:p491 + u13:p492 + u13:p493 + u13:p494 + u13:p495 + u13:p496 + u13:p497 + u13:p498 + u13:p499 + u13:p500 + u13:p501 + u13:p502 + u13:p503 + u13:p504 + u13:p505 + u13:p506 + u13:p507 + u13:p508 + u13:p509 + u13:p510 + u13:p511 + u26:p3 + u25:p2 + u24:p1 + u22:p0 = 1

invariant :u11:p260 + u11:p261 + u11:p262 + u11:p263 + u11:p264 + u11:p265 + u11:p266 + u11:p267 + u11:p268 + u11:p269 + u11:p270 + u11:p271 + u11:p272 + u11:p273 + u11:p274 + u11:p275 + u11:p276 + u11:p277 + u11:p278 + u11:p279 + u11:p280 + u11:p281 + u11:p282 + u11:p283 + u11:p284 + u11:p285 + u11:p286 + u11:p287 + u11:p288 + u11:p289 + u11:p290 + u11:p291 + u11:p292 + u11:p293 + u11:p294 + u11:p295 + u11:p296 + u11:p297 + u11:p298 + u11:p299 + u11:p300 + u11:p301 + u11:p302 + u11:p303 + u11:p304 + u11:p305 + u11:p306 + u11:p307 + u11:p308 + u11:p309 + u11:p310 + u11:p311 + u11:p312 + u11:p313 + u11:p314 + u11:p315 + u11:p316 + u11:p317 + u11:p318 + u11:p319 + u11:p320 + u11:p321 + u11:p322 + u11:p323 + u11:p324 + u11:p325 + u11:p326 + u11:p327 + u11:p328 + u11:p329 + u11:p330 + u11:p331 + u11:p332 + u11:p333 + u11:p334 + u11:p335 + u11:p336 + u11:p337 + u11:p338 + u11:p339 + u11:p340 + u11:p341 + u11:p342 + u11:p343 + u19:p5 + u27:p4 + u26:p3 + u25:p2 + u24:p1 + u22:p0 = 1

invariant :u12:p344 + u12:p345 + u12:p346 + u12:p347 + u12:p348 + u12:p349 + u12:p350 + u12:p351 + u12:p352 + u12:p353 + u12:p354 + u12:p355 + u12:p356 + u12:p357 + u12:p358 + u12:p359 + u12:p360 + u12:p361 + u12:p362 + u12:p363 + u12:p364 + u12:p365 + u12:p366 + u12:p367 + u12:p368 + u12:p369 + u12:p370 + u12:p371 + u12:p372 + u12:p373 + u12:p374 + u12:p375 + u12:p376 + u12:p377 + u12:p378 + u12:p379 + u12:p380 + u12:p381 + u12:p382 + u12:p383 + u12:p384 + u12:p385 + u12:p386 + u12:p387 + u12:p388 + u12:p389 + u12:p390 + u12:p391 + u12:p392 + u12:p393 + u12:p394 + u12:p395 + u12:p396 + u12:p397 + u12:p398 + u12:p399 + u12:p400 + u12:p401 + u12:p402 + u12:p403 + u12:p404 + u12:p405 + u12:p406 + u12:p407 + u12:p408 + u12:p409 + u12:p410 + u12:p411 + u12:p412 + u12:p413 + u12:p414 + u12:p415 + u12:p416 + u12:p417 + u12:p418 + u12:p419 + u12:p420 + u12:p421 + u12:p422 + u12:p423 + u12:p424 + u12:p425 + u12:p426 + u12:p427 + u27:p4 + u26:p3 + u25:p2 + u24:p1 + u22:p0 = 1

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O3, model.c], workingDir=/home/mcc/execution]

Compilation finished in 9770 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 122 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (<>([]((LTLAP0==true))))U(((LTLAP1==true))U((LTLAP2==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 3780 ms.

FORMULA FlexibleBarrier-PT-08b-LTLCardinality-00 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, (X((LTLAP3==true)))U(((LTLAP4==true))U((LTLAP5==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 77 ms.

FORMULA FlexibleBarrier-PT-08b-LTLCardinality-01 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(([]((LTLAP6==true)))U([]((LTLAP7==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

WARNING : LTSmin timed out (>225 s) on command CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(([]((LTLAP6==true)))U([]((LTLAP7==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(X(<>(<>((LTLAP8==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 105 ms.

FORMULA FlexibleBarrier-PT-08b-LTLCardinality-03 TRUE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (LTLAP9==true), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 3576 ms.

FORMULA FlexibleBarrier-PT-08b-LTLCardinality-04 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (LTLAP10==true), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 3491 ms.

FORMULA FlexibleBarrier-PT-08b-LTLCardinality-05 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, <>([](((LTLAP11==true))U((LTLAP12==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 3550 ms.

FORMULA FlexibleBarrier-PT-08b-LTLCardinality-06 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, []([]((LTLAP13==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

WARNING : LTSmin timed out (>225 s) on command CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, []([]((LTLAP13==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (<>(<>((LTLAP14==true))))U([]([]((LTLAP15==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

WARNING : LTS min runner thread failed on error :java.lang.RuntimeException: Unexpected exception when executing ltsmin :CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (<>(<>((LTLAP14==true))))U([]([]((LTLAP15==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

255

sparsehash FATAL ERROR: failed to allocate 39 groups

BK_STOP 1527961269040

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution LTLCardinality -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination LTLCardinality -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLCardinality, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 87 ms

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 920 places.

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 1057 transitions.

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

Jun 02, 2018 5:30:29 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 21 ms

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.application.MccTranslator applyOrder

INFO: Applying decomposition

Jun 02, 2018 5:30:29 PM fr.lip6.move.gal.instantiate.CompositeBuilder decomposeWithOrder

INFO: Decomposing Gal with order

Jun 02, 2018 5:30:30 PM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 130 ms

Jun 02, 2018 5:30:30 PM fr.lip6.move.gal.instantiate.CompositeBuilder rewriteArraysToAllowPartition

INFO: Rewriting arrays to variables to allow decomposition.

Jun 02, 2018 5:30:30 PM fr.lip6.move.gal.instantiate.Instantiator fuseIsomorphicEffects

INFO: Removed a total of 49 redundant transitions.

Jun 02, 2018 5:30:30 PM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/LTLCardinality.pnml.gal : 8 ms

Jun 02, 2018 5:30:30 PM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSLTLTools

INFO: Time to serialize properties into /home/mcc/execution/LTLCardinality.ltl : 1 ms

Jun 02, 2018 5:30:30 PM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 1057 transitions.

Jun 02, 2018 5:30:31 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 10 place invariants in 280 ms

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 920 variables to be positive in 1137 ms

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 1057 transitions.

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/1057 took 0 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 116 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 1057 transitions.

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 74 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 02, 2018 5:30:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 1057 transitions.

Jun 02, 2018 5:30:35 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(11/1057) took 2682 ms. Total solver calls (SAT/UNSAT): 5601(18/5583)

Jun 02, 2018 5:30:40 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(18/1057) took 7147 ms. Total solver calls (SAT/UNSAT): 6643(85/6558)

Jun 02, 2018 5:30:45 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(20/1057) took 12929 ms. Total solver calls (SAT/UNSAT): 6942(138/6804)

Jun 02, 2018 5:30:49 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(22/1057) took 16795 ms. Total solver calls (SAT/UNSAT): 7237(187/7050)

Jun 02, 2018 5:30:54 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(24/1057) took 21248 ms. Total solver calls (SAT/UNSAT): 7528(232/7296)

Jun 02, 2018 5:30:58 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(27/1057) took 25527 ms. Total solver calls (SAT/UNSAT): 7921(295/7626)

Jun 02, 2018 5:31:01 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(29/1057) took 28639 ms. Total solver calls (SAT/UNSAT): 8202(332/7870)

Jun 02, 2018 5:31:05 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(31/1057) took 32262 ms. Total solver calls (SAT/UNSAT): 8479(365/8114)

Jun 02, 2018 5:31:09 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(34/1057) took 36293 ms. Total solver calls (SAT/UNSAT): 8851(409/8442)

Jun 02, 2018 5:31:12 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(37/1057) took 39296 ms. Total solver calls (SAT/UNSAT): 9250(445/8805)

Jun 02, 2018 5:31:15 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(40/1057) took 42566 ms. Total solver calls (SAT/UNSAT): 9640(472/9168)

Jun 02, 2018 5:31:18 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(46/1057) took 45958 ms. Total solver calls (SAT/UNSAT): 10357(505/9852)

SMT solver raised 'unknown', retrying with same input.

SMT solver raised 'unknown' twice, overapproximating result to 1.

Jun 02, 2018 5:31:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(49/1057) took 50827 ms. Total solver calls (SAT/UNSAT): 10601(509/10092)

Jun 02, 2018 5:31:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 50878 ms. Total solver calls (SAT/UNSAT): 10601(509/10092)

Jun 02, 2018 5:31:23 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 1057 transitions.

Jun 02, 2018 5:31:32 PM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Completed DNA matrix. took 8332 ms. Total solver calls (SAT/UNSAT): 7715(0/7715)

Jun 02, 2018 5:31:32 PM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 61951ms conformant to PINS in folder :/home/mcc/execution

pins2lts-mc, 0.000: Registering PINS so language module

pins2lts-mc, 0.000, ** error **: out of memory trying to get 4294967296

java.lang.RuntimeException: Unexpected exception when executing ltsmin :CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (<>(<>((LTLAP14==true))))U([]([]((LTLAP15==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

255

at fr.lip6.move.gal.application.LTSminRunner.checkProperty(LTSminRunner.java:167)

at fr.lip6.move.gal.application.LTSminRunner.access$9(LTSminRunner.java:122)

at fr.lip6.move.gal.application.LTSminRunner$1.run(LTSminRunner.java:91)

at java.lang.Thread.run(Thread.java:748)

ITS-tools command line returned an error code 1

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="FlexibleBarrier-PT-08b"

export BK_EXAMINATION="LTLCardinality"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/FlexibleBarrier-PT-08b.tgz

mv FlexibleBarrier-PT-08b execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstools"

echo " Input is FlexibleBarrier-PT-08b, examination is LTLCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r248-blw7-152732549700039"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;