About the Execution of ITS-Tools for DNAwalker-PT-07track28RR

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 15754.980 | 25104.00 | 52104.00 | 511.40 | FFFTFFFFFFFFFFFF | normal |

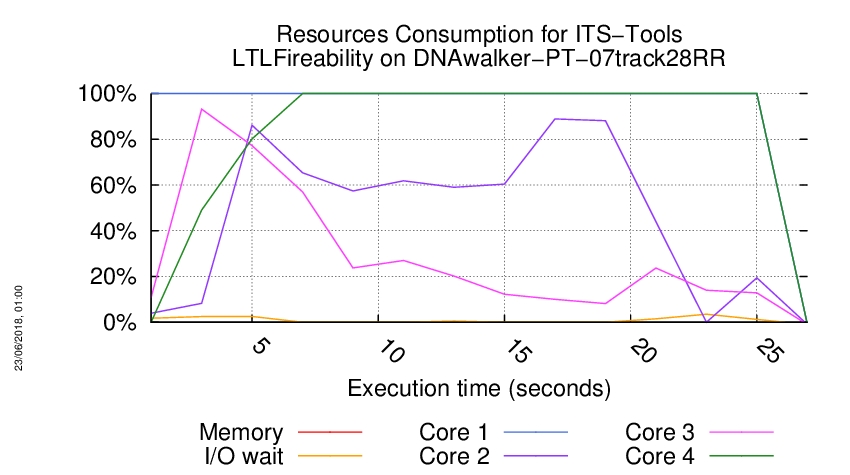

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

....................

/home/mcc/execution

total 280K

-rw-r--r-- 1 mcc users 3.8K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 22K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.6K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.5K May 26 09:26 LTLCardinality.txt

-rw-r--r-- 1 mcc users 11K May 26 09:26 LTLCardinality.xml

-rw-r--r-- 1 mcc users 2.0K May 26 09:26 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.9K May 26 09:26 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.8K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 115 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 353 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 3.1K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.7K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.8K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 12 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 108K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool itstools

Input is DNAwalker-PT-07track28RR, examination is LTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r212-smll-152732263000240

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-00

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-01

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-02

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-03

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-04

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-05

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-06

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-07

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-08

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-09

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-10

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-11

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-12

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-13

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-14

FORMULA_NAME DNAwalker-PT-07track28RR-LTLFireability-15

=== Now, execution of the tool begins

BK_START 1527934853584

Using solver Z3 to compute partial order matrices.

Built C files in :

/home/mcc/execution

Invoking ITS tools like this :CommandLine [args=[/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ltl-linux64, --gc-threshold, 2000000, -i, /home/mcc/execution/LTLFireability.pnml.gal, -t, CGAL, -LTL, /home/mcc/execution/LTLFireability.ltl, -c, -stutter-deadlock], workingDir=/home/mcc/execution]

its-ltl command run as :

/home/mcc/BenchKit/itstools/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201805151631/bin/its-ltl-linux64 --gc-threshold 2000000 -i /home/mcc/execution/LTLFireability.pnml.gal -t CGAL -LTL /home/mcc/execution/LTLFireability.ltl -c -stutter-deadlock

Read 16 LTL properties

Checking formula 0 : !((("((A13>=2)&&(A16>=1))")U(X(("((A1>=2)&&(A2>=1))")U("((A5>=2)&&(A13>=1))")))))

Formula 0 simplified : !("((A13>=2)&&(A16>=1))" U X("((A1>=2)&&(A2>=1))" U "((A5>=2)&&(A13>=1))"))

Presburger conditions satisfied. Using coverability to approximate state space in K-Induction.

Normalized transition count is 247

// Phase 1: matrix 247 rows 34 cols

Reverse transition relation is NOT exact ! Due to transitions tb5, tAb5, tb6, tAb6, tb15, tAb15, tb16, tAb16, tb23, tAb23, tb24, tAb24, t1_2, t1_3, t1_4, t1_5, t1_9, t2_3, t2_4, t2_5, t2_6, t2_9, t2_10, t3_2, t3_4, t3_5, t3_6, t3_7, t3_9, t3_10, t3_11, t4_2, t4_3, t4_5, t4_6, t4_7, t4_9, t4_10, t4_11, t5_2, t5_3, t5_4, t5_6, t5_7, t5_8, t5_9, t5_10, t5_11, t5_13, t6_2, t6_3, t6_4, t6_5, t6_7, t6_8, t6_9, t6_10, t6_13, t6_14, t6_18, t6_19, t7_3, t7_4, t7_5, t7_6, t7_8, t7_9, t7_13, t7_14, t7_15, t7_18, t7_19, t8_5, t8_6, t8_7, t8_13, t8_14, t8_15, t8_16, t8_18, t8_19, t9_2, t9_3, t9_4, t9_5, t9_6, t9_7, t9_10, t9_11, t9_12, t9_21, t10_3, t10_4, t10_5, t10_6, t10_9, t10_11, t10_12, t10_21, t10_22, t10_23, t10_24, t11_3, t11_4, t11_5, t11_9, t11_10, t11_12, t11_21, t11_22, t11_23, t11_24, t11_26, t12_9, t12_10, t12_11, t12_21, t12_22, t12_23, t12_24, t12_26, t12_27, t13_5, t13_6, t13_7, t13_8, t13_14, t13_15, t13_16, t13_17, t13_18, t13_19, t13_20, t14_19, t14_20, t15_7, t15_8, t15_13, t15_14, t15_16, t15_17, t15_18, t15_19, t15_20, t16_8, t16_13, t16_14, t16_15, t16_17, t16_18, t16_19, t18_19, t18_20, t18_25, t19_6, t19_7, t19_8, t19_13, t19_14, t19_15, t19_16, t19_18, t19_20, t19_24, t19_25, t21_9, t21_10, t21_11, t21_12, t21_22, t21_23, t21_24, t21_25, t21_26, t21_27, t21_28, t22_10, t22_11, t22_12, t22_21, t22_23, t22_24, t22_25, t22_26, t22_27, t22_28, t23_10, t23_11, t23_12, t23_20, t23_21, t23_22, t23_24, t23_25, t23_26, t23_27, t23_28, t24_10, t24_11, t24_12, t24_19, t24_20, t24_21, t24_22, t24_23, t24_25, t24_26, t24_27, t26_12, t26_21, t26_22, t26_23, t26_24, t26_25, t26_28, t27_24, Intersection with reachable at each step enabled. (destroyed/reverse/intersect/total) :5/29/216/250

Computing Next relation with stutter on 106288 deadlock states

10 unique states visited

10 strongly connected components in search stack

10 transitions explored

10 items max in DFS search stack

600 ticks for the emptiness check

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

STATS,0,6.04044,134116,1,0,793,637174,530,336,2823,617464,710

an accepting run exists (use option '-e' to print it)

Formula 0 is FALSE accepting run found.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-00 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Checking formula 1 : !((G(F(F(G(X("(B5>=1)")))))))

Formula 1 simplified : !GFGX"(B5>=1)"

Computing Next relation with stutter on 106288 deadlock states

34 unique states visited

33 strongly connected components in search stack

36 transitions explored

34 items max in DFS search stack

891 ticks for the emptiness check

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

STATS,0,14.941,294572,1,0,887,1.31535e+06,535,505,2824,1.73919e+06,1084

an accepting run exists (use option '-e' to print it)

Formula 1 is FALSE accepting run found.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-01 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Checking formula 2 : !((G(F("((A23>=2)&&(A24>=1))"))))

Formula 2 simplified : !GF"((A23>=2)&&(A24>=1))"

Computing Next relation with stutter on 106288 deadlock states

33 unique states visited

33 strongly connected components in search stack

34 transitions explored

33 items max in DFS search stack

11 ticks for the emptiness check

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

STATS,0,15.0583,295884,1,0,944,1.32094e+06,544,552,2827,1.7625e+06,1237

an accepting run exists (use option '-e' to print it)

Formula 2 is FALSE accepting run found.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-02 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Checking formula 3 : !(("(B24>=1)"))

Formula 3 simplified : !"(B24>=1)"

Computing Next relation with stutter on 106288 deadlock states

1 unique states visited

0 strongly connected components in search stack

0 transitions explored

1 items max in DFS search stack

0 ticks for the emptiness check

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

STATS,0,15.0595,295884,1,0,944,1.32094e+06,547,552,2828,1.7625e+06,1239

no accepting run found

Formula 3 is TRUE no accepting run found.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-03 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Checking formula 4 : !((X(F("((A4>=2)&&(A7>=1))"))))

Formula 4 simplified : !XF"((A4>=2)&&(A7>=1))"

Computing Next relation with stutter on 106288 deadlock states

Running compilation step : CommandLine [args=[gcc, -c, -I/home/mcc/BenchKit//lts_install_dir//include, -I., -std=c99, -fPIC, -O3, model.c], workingDir=/home/mcc/execution]

Compilation finished in 3877 ms.

Running link step : CommandLine [args=[gcc, -shared, -o, gal.so, model.o], workingDir=/home/mcc/execution]

Link finished in 46 ms.

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(<>((LTLAP6==true))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 34 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-04 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(((LTLAP7==true))U(((LTLAP8==true))U((LTLAP9==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 17 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-05 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, (<>((LTLAP10==true)))U([](X(X((LTLAP11==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 29 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-06 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, <>(X((<>((LTLAP12==true)))U([]((LTLAP13==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 25 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-07 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (((LTLAP14==true))U((LTLAP15==true)))U((LTLAP16==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 71 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-08 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, <>((<>((LTLAP17==true)))U(((LTLAP18==true))U((LTLAP19==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 68 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-09 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, []((LTLAP9==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 69 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-10 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X(X(X(((LTLAP20==true))U((LTLAP21==true))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 30 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-11 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, X((LTLAP22==true)), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 24 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-12 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, <>(X([]((LTLAP23==true)))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 24 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-13 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, --when, --ltl, []([](X(<>([]((LTLAP24==true)))))), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 24 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-14 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

Running LTSmin : CommandLine [args=[/home/mcc/BenchKit//lts_install_dir//bin/pins2lts-mc, ./gal.so, --threads=1, -p, --pins-guards, --when, --ltl, (LTLAP25==true), --buchi-type=spotba], workingDir=/home/mcc/execution]

LTSmin run took 71 ms.

FORMULA DNAwalker-PT-07track28RR-LTLFireability-15 FALSE TECHNIQUES PARTIAL_ORDER EXPLICIT LTSMIN SAT_SMT

ITS tools runner thread asked to quit. Dying gracefully.

BK_STOP 1527934878688

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ /home/mcc/BenchKit//runeclipse.sh /home/mcc/execution LTLFireability -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt

+ ulimit -s 65536

+ [[ -z '' ]]

+ export LTSMIN_MEM_SIZE=8589934592

+ LTSMIN_MEM_SIZE=8589934592

+ /home/mcc/BenchKit//itstools/its-tools -consoleLog -data /home/mcc/execution/workspace -pnfolder /home/mcc/execution -examination LTLFireability -z3path /home/mcc/BenchKit//z3/bin/z3 -yices2path /home/mcc/BenchKit//yices/bin/yices -its -ltsminpath /home/mcc/BenchKit//lts_install_dir/ -smt -vmargs -Dosgi.locking=none -Declipse.stateSaveDelayInterval=-1 -Dosgi.configuration.area=/tmp/.eclipse -Xss8m -Xms40m -Xmx8192m -Dfile.encoding=UTF-8 -Dosgi.requiredJavaVersion=1.6

Jun 02, 2018 10:20:56 AM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-pnfolder, /home/mcc/execution, -examination, LTLFireability, -z3path, /home/mcc/BenchKit//z3/bin/z3, -yices2path, /home/mcc/BenchKit//yices/bin/yices, -its, -ltsminpath, /home/mcc/BenchKit//lts_install_dir/, -smt]

Jun 02, 2018 10:20:56 AM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /home/mcc/execution/model.pnml

Jun 02, 2018 10:20:56 AM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 87 ms

Jun 02, 2018 10:20:56 AM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 34 places.

Jun 02, 2018 10:20:56 AM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 250 transitions.

Jun 02, 2018 10:20:56 AM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/model.pnml.img.gal : 26 ms

Jun 02, 2018 10:20:56 AM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 97 ms

Jun 02, 2018 10:20:56 AM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /home/mcc/execution/LTLFireability.pnml.gal : 6 ms

Jun 02, 2018 10:20:56 AM fr.lip6.move.serialization.SerializationUtil serializePropertiesForITSLTLTools

INFO: Time to serialize properties into /home/mcc/execution/LTLFireability.ltl : 1 ms

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 250 transitions.

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver computeAndDeclareInvariants

INFO: Computed 0 place invariants in 24 ms

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.KInductionSolver init

INFO: Proved 34 variables to be positive in 244 ms

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may disable matrix : 250 transitions.

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of disable matrix completed :0/250 took 1 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete disable matrix. took 64 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeAblingMatrix

INFO: Computing symmetric may enable matrix : 250 transitions.

Jun 02, 2018 10:20:57 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Complete enable matrix. took 18 ms. Total solver calls (SAT/UNSAT): 0(0/0)

Jun 02, 2018 10:21:00 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeCoEnablingMatrix

INFO: Computing symmetric co enabling matrix : 250 transitions.

Jun 02, 2018 10:21:00 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(9/250) took 128 ms. Total solver calls (SAT/UNSAT): 5(5/0)

Jun 02, 2018 10:21:03 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(105/250) took 3140 ms. Total solver calls (SAT/UNSAT): 2169(2169/0)

Jun 02, 2018 10:21:06 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of co-enabling matrix(225/250) took 6144 ms. Total solver calls (SAT/UNSAT): 3900(3900/0)

Jun 02, 2018 10:21:07 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Finished co-enabling matrix. took 6538 ms. Total solver calls (SAT/UNSAT): 4015(4015/0)

Jun 02, 2018 10:21:07 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver computeDoNotAccord

INFO: Computing Do-Not-Accords matrix : 250 transitions.

Jun 02, 2018 10:21:12 AM fr.lip6.move.gal.gal2smt.bmc.NecessaryEnablingsolver printStats

INFO: Computation of Completed DNA matrix. took 5554 ms. Total solver calls (SAT/UNSAT): 1055(0/1055)

Jun 02, 2018 10:21:13 AM fr.lip6.move.gal.gal2pins.Gal2PinsTransformerNext transform

INFO: Built C files in 15998ms conformant to PINS in folder :/home/mcc/execution

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DNAwalker-PT-07track28RR"

export BK_EXAMINATION="LTLFireability"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DNAwalker-PT-07track28RR.tgz

mv DNAwalker-PT-07track28RR execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool itstools"

echo " Input is DNAwalker-PT-07track28RR, examination is LTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r212-smll-152732263000240"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "LTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "LTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "LTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property LTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "LTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;