About the Execution of Irma.struct for DLCshifumi-PT-5a

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 3581.300 | 154166.00 | 153528.00 | 1015.40 | TFTFTFFTFTFFFTTF | normal |

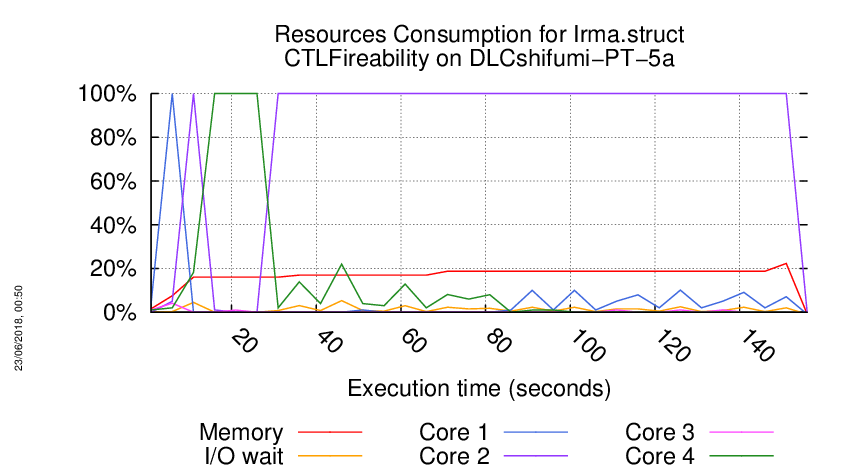

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

..............................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 4.1M

-rw-r--r-- 1 mcc users 3.7K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 21K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.9K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 20K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 6.0K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.6K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 13K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.6K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.4K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 17K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 107 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 345 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.5K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 14K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.7K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 3 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 3.9M May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool irma4mcc-structural

Input is DLCshifumi-PT-5a, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r067-smll-152649739700200

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-00

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-01

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-02

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-03

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-04

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-05

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-06

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-07

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-08

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-09

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-10

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-11

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-12

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-13

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-14

FORMULA_NAME DLCshifumi-PT-5a-CTLFireability-15

=== Now, execution of the tool begins

BK_START 1526656883493

BK_STOP 1526657037659

--------------------

content from stderr:

Prefix is 75f5f979.

Reading known information in /usr/share/mcc4mcc/75f5f979-known.json.

Reading learned information in /usr/share/mcc4mcc/75f5f979-learned.json.

Reading value translations in /usr/share/mcc4mcc/75f5f979-values.json.

Using directory /home/mcc/execution for input, as it contains a model.pnml file.

Using DLCshifumi-PT-5a as instance name.

Using DLCshifumi as model name.

Using algorithm or tool bmdt.

Model characteristics are: {'Examination': 'CTLFireability', 'Place/Transition': True, 'Colored': False, 'Relative-Time': 1, 'Relative-Memory': 1, 'Ordinary': True, 'Simple Free Choice': False, 'Extended Free Choice': False, 'State Machine': False, 'Marked Graph': False, 'Connected': True, 'Strongly Connected': False, 'Source Place': True, 'Sink Place': False, 'Source Transition': False, 'Sink Transition': False, 'Loop Free': None, 'Conservative': False, 'Sub-Conservative': False, 'Nested Units': True, 'Safe': True, 'Deadlock': None, 'Reversible': None, 'Quasi Live': None, 'Live': None}.

Known tools are: [{'Time': 186475, 'Memory': 2690.34, 'Tool': 'marcie'}, {'Time': 189444, 'Memory': 2690.5, 'Tool': 'marcie'}, {'Time': 1242951, 'Memory': 15944.78, 'Tool': 'lola'}, {'Time': 1244596, 'Memory': 15947.89, 'Tool': 'lola'}, {'Time': 3521882, 'Memory': 10115.63, 'Tool': 'itstools'}, {'Time': 3522079, 'Memory': 9122.29, 'Tool': 'itstools'}].

Learned tools are: [{'Tool': 'itstools'}].

Learned tool itstools is 18.886617509049472x far from the best tool marcie.

CTLFireability marcie DLCshifumi-PT-5a...

timeout --kill-after=10s --signal=SIGINT 1m for testing only

Marcie rev. 8852M (built: crohr on 2017-05-03)

A model checker for Generalized Stochastic Petri nets

authors: Alex Tovchigrechko (IDD package and CTL model checking)

Martin Schwarick (Symbolic numerical analysis and CSL model checking)

Christian Rohr (Simulative and approximative numerical model checking)

marcie@informatik.tu-cottbus.de

called as: marcie --net-file=model.pnml --mcc-file=CTLFireability.xml --memory=6

parse successfull

net created successfully

Net: DLCshifumi_PT_5a

(NrP: 2162 NrTr: 14865 NrArc: 57457)

check for maximal unmarked siphon

ok

check for constant places

ok

check if there are places and transitions

ok

check if there are transitions without pre-places

parse formulas

formulas created successfully

place and transition orderings generation:0m 0.040sec

ok

check if at least one transition is enabled in m0

ok

check if there are transitions that can never fire

ok

net check time: 0m 0.011sec

init dd package: 0m 1.606sec

RS generation: 0m 4.023sec

-> reachability set: #nodes 2162 (2.2e+03) #states 8,852,357,036,934,680,168,443,581,137,271,812,758,567,006,111,470,214,493,356,924,526,009,325,372,899,988,098,142,188,147,370,936,549,634,300,001 (108)

starting MCC model checker

--------------------------

checking: AX [AF [IS_FIREABLE [t4512]]]

normalized: ~ [EX [EG [~ [IS_FIREABLE [t4512]]]]]

.

EG iterations: 1

.-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-08 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 7.672sec

checking: ~ [AG [EF [~ [IS_FIREABLE [t1939]]]]]

normalized: E [true U ~ [E [true U ~ [IS_FIREABLE [t1939]]]]]

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-11 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.746sec

checking: A [IS_FIREABLE [t9149] U EG [~ [IS_FIREABLE [t1982]]]]

normalized: [~ [EG [~ [EG [~ [IS_FIREABLE [t1982]]]]]] & ~ [E [~ [EG [~ [IS_FIREABLE [t1982]]]] U [~ [IS_FIREABLE [t9149]] & ~ [EG [~ [IS_FIREABLE [t1982]]]]]]]]

.

EG iterations: 1

.

EG iterations: 1

.

EG iterations: 1

.

EG iterations: 1

-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-00 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 7.897sec

checking: ~ [~ [EG [~ [[IS_FIREABLE [t669] & IS_FIREABLE [t10425]]]]]]

normalized: EG [~ [[IS_FIREABLE [t669] & IS_FIREABLE [t10425]]]]

.

EG iterations: 1

-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-04 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 2.413sec

checking: ~ [A [AX [IS_FIREABLE [t6661]] U EG [IS_FIREABLE [t9182]]]]

normalized: ~ [[~ [EG [~ [EG [IS_FIREABLE [t9182]]]]] & ~ [E [~ [EG [IS_FIREABLE [t9182]]] U [EX [~ [IS_FIREABLE [t6661]]] & ~ [EG [IS_FIREABLE [t9182]]]]]]]]

.

EG iterations: 1

after gc: zbdd nodes used:5193, unused:18744807..

EG iterations: 1

.

EG iterations: 1

..

EG iterations: 2

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-05 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 9.444sec

checking: EF [[IS_FIREABLE [t6302] & IS_FIREABLE [t4919]]]

normalized: E [true U [IS_FIREABLE [t6302] & IS_FIREABLE [t4919]]]

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-12 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.061sec

checking: EF [[EX [[IS_FIREABLE [t10896] | IS_FIREABLE [t1678]]] & ~ [AF [IS_FIREABLE [t79]]]]]

normalized: E [true U [EG [~ [IS_FIREABLE [t79]]] & EX [[IS_FIREABLE [t10896] | IS_FIREABLE [t1678]]]]]

..

EG iterations: 1

-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-02 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 7.708sec

checking: AG [[EF [[IS_FIREABLE [t4850] | IS_FIREABLE [t13234]]] & EF [~ [IS_FIREABLE [t13113]]]]]

normalized: ~ [E [true U ~ [[E [true U ~ [IS_FIREABLE [t13113]]] & E [true U [IS_FIREABLE [t4850] | IS_FIREABLE [t13234]]]]]]]

-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-09 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 3.599sec

checking: [[EG [AG [IS_FIREABLE [t9390]]] | [IS_FIREABLE [t4477] & IS_FIREABLE [t9411]]] | AF [IS_FIREABLE [t5300]]]

normalized: [~ [EG [~ [IS_FIREABLE [t5300]]]] | [[IS_FIREABLE [t4477] & IS_FIREABLE [t9411]] | EG [~ [E [true U ~ [IS_FIREABLE [t9390]]]]]]]

.

EG iterations: 1

.

EG iterations: 1

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-10 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 3.892sec

checking: EG [[[[~ [IS_FIREABLE [t3266]] | [IS_FIREABLE [t12941] & IS_FIREABLE [t5819]]] | IS_FIREABLE [t2375]] | IS_FIREABLE [t11769]]]

normalized: EG [[IS_FIREABLE [t11769] | [IS_FIREABLE [t2375] | [[IS_FIREABLE [t12941] & IS_FIREABLE [t5819]] | ~ [IS_FIREABLE [t3266]]]]]]

.

EG iterations: 1

-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-14 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 2.518sec

checking: [[EG [IS_FIREABLE [t3457]] & IS_FIREABLE [t10654]] | EG [[[~ [IS_FIREABLE [t12057]] & [IS_FIREABLE [t14859] & IS_FIREABLE [t4300]]] | ~ [IS_FIREABLE [t9501]]]]]

normalized: [EG [[~ [IS_FIREABLE [t9501]] | [[IS_FIREABLE [t14859] & IS_FIREABLE [t4300]] & ~ [IS_FIREABLE [t12057]]]]] | [IS_FIREABLE [t10654] & EG [IS_FIREABLE [t3457]]]]

.

EG iterations: 1

.

EG iterations: 1

-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-13 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 4.442sec

checking: [~ [EF [[IS_FIREABLE [t1181] & ~ [IS_FIREABLE [t3044]]]]] & [[IS_FIREABLE [t12705] | E [IS_FIREABLE [t10702] U IS_FIREABLE [t5788]]] | [[~ [~ [IS_FIREABLE [t14265]]] | AF [IS_FIREABLE [t14446]]] | ~ [IS_FIREABLE [t5209]]]]]

normalized: [[[~ [IS_FIREABLE [t5209]] | [IS_FIREABLE [t14265] | ~ [EG [~ [IS_FIREABLE [t14446]]]]]] | [IS_FIREABLE [t12705] | E [IS_FIREABLE [t10702] U IS_FIREABLE [t5788]]]] & ~ [E [true U [IS_FIREABLE [t1181] & ~ [IS_FIREABLE [t3044]]]]]]

after gc: zbdd nodes used:4804, unused:37495196..

EG iterations: 2

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-03 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m12.343sec

checking: [[IS_FIREABLE [t2901] & [[AX [IS_FIREABLE [t12401]] | IS_FIREABLE [t10532]] | EF [IS_FIREABLE [t9049]]]] | [EG [EG [IS_FIREABLE [t7839]]] | A [~ [IS_FIREABLE [t2917]] U [IS_FIREABLE [t3405] & IS_FIREABLE [t1109]]]]]

normalized: [[[~ [EG [~ [[IS_FIREABLE [t3405] & IS_FIREABLE [t1109]]]]] & ~ [E [~ [[IS_FIREABLE [t3405] & IS_FIREABLE [t1109]]] U [IS_FIREABLE [t2917] & ~ [[IS_FIREABLE [t3405] & IS_FIREABLE [t1109]]]]]]] | EG [EG [IS_FIREABLE [t7839]]]] | [IS_FIREABLE [t2901] & [E [true U IS_FIREABLE [t9049]] | [IS_FIREABLE [t10532] | ~ [EX [~ [IS_FIREABLE [t12401]]]]]]]]

..

EG iterations: 1

.

EG iterations: 1

.

EG iterations: 1

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-15 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m33.747sec

checking: [[E [~ [IS_FIREABLE [t13891]] U IS_FIREABLE [t14342]] | [[[[IS_FIREABLE [t13822] | IS_FIREABLE [t3926]] & ~ [IS_FIREABLE [t3400]]] | AF [IS_FIREABLE [t9540]]] & [~ [[IS_FIREABLE [t13030] | IS_FIREABLE [t1701]]] | AF [IS_FIREABLE [t4503]]]]] | EG [AF [[IS_FIREABLE [t3898] | IS_FIREABLE [t2054]]]]]

normalized: [EG [~ [EG [~ [[IS_FIREABLE [t3898] | IS_FIREABLE [t2054]]]]]] | [[[~ [EG [~ [IS_FIREABLE [t4503]]]] | ~ [[IS_FIREABLE [t13030] | IS_FIREABLE [t1701]]]] & [~ [EG [~ [IS_FIREABLE [t9540]]]] | [~ [IS_FIREABLE [t3400]] & [IS_FIREABLE [t13822] | IS_FIREABLE [t3926]]]]] | E [~ [IS_FIREABLE [t13891]] U IS_FIREABLE [t14342]]]]

.

EG iterations: 1

.

EG iterations: 1

.

EG iterations: 1

.

EG iterations: 1

-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-01 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m13.193sec

checking: [A [AF [IS_FIREABLE [t5621]] U [[IS_FIREABLE [t7625] | IS_FIREABLE [t14288]] | [IS_FIREABLE [t13311] | IS_FIREABLE [t13856]]]] | [[[[IS_FIREABLE [t4874] | IS_FIREABLE [t4474]] & EX [IS_FIREABLE [t2280]]] & [EX [IS_FIREABLE [t9396]] | EF [IS_FIREABLE [t11371]]]] & IS_FIREABLE [t13603]]]

normalized: [[IS_FIREABLE [t13603] & [[E [true U IS_FIREABLE [t11371]] | EX [IS_FIREABLE [t9396]]] & [EX [IS_FIREABLE [t2280]] & [IS_FIREABLE [t4874] | IS_FIREABLE [t4474]]]]] | [~ [EG [~ [[[IS_FIREABLE [t13311] | IS_FIREABLE [t13856]] | [IS_FIREABLE [t7625] | IS_FIREABLE [t14288]]]]]] & ~ [E [~ [[[IS_FIREABLE [t13311] | IS_FIREABLE [t13856]] | [IS_FIREABLE [t7625] | IS_FIREABLE [t14288]]]] U [EG [~ [IS_FIREABLE [t5621]]] & ~ [[[IS_FIREABLE [t13311] | IS_FIREABLE [t13856]] | [IS_FIREABLE [t7625] | IS_FIREABLE [t14288]]]]]]]]]

.

EG iterations: 1

..

EG iterations: 2

..-> the formula is FALSE

FORMULA DLCshifumi-PT-5a-CTLFireability-06 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m13.807sec

checking: E [[AG [IS_FIREABLE [t11082]] | ~ [[IS_FIREABLE [t13011] & IS_FIREABLE [t4750]]]] U [[[IS_FIREABLE [t4860] & IS_FIREABLE [t12098]] | [IS_FIREABLE [t8437] & IS_FIREABLE [t14360]]] & [[IS_FIREABLE [t13188] & IS_FIREABLE [t5463]] & [IS_FIREABLE [t1385] & IS_FIREABLE [t6958]]]]]

normalized: E [[~ [[IS_FIREABLE [t13011] & IS_FIREABLE [t4750]]] | ~ [E [true U ~ [IS_FIREABLE [t11082]]]]] U [[[IS_FIREABLE [t1385] & IS_FIREABLE [t6958]] & [IS_FIREABLE [t13188] & IS_FIREABLE [t5463]]] & [[IS_FIREABLE [t8437] & IS_FIREABLE [t14360]] | [IS_FIREABLE [t4860] & IS_FIREABLE [t12098]]]]]

after gc: zbdd nodes used:6348, unused:74993652-> the formula is TRUE

FORMULA DLCshifumi-PT-5a-CTLFireability-07 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m18.675sec

totally nodes used: 67363506(6.7e+07)

number of garbage collections: 3

fire ops cache: hits/miss/sum: 494165593 619195347 1113360940

used/not used/entry size/cache size: 22053364 45055500 16 1024MB

basic ops cache: hits/miss/sum: 52522724 60280240 112802964

used/not used/entry size/cache size: 2957399 13819817 12 192MB

unary ops cache: hits/miss/sum: 0 0 0

used/not used/entry size/cache size: 0 8388608 8 64MB

abstract ops cache: hits/miss/sum: 0 0 0

used/not used/entry size/cache size: 0 8388608 12 96MB

state nr cache: hits/miss/sum: 783 2162 2945

used/not used/entry size/cache size: 0 2097152 32 64MB

max state cache: hits/miss/sum: 0 0 0

used/not used/entry size/cache size: 0 8388608 32 256MB

uniqueHash elements/entry size/size: 67108864 4 256MB

0 65376264

1 1710533

2 21884

3 182

4 1

5 0

6 0

7 0

8 0

9 0

>= 10 0

Total processing time: 2m29.639sec

.................................................

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCshifumi-PT-5a"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="irma4mcc-structural"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DLCshifumi-PT-5a.tgz

mv DLCshifumi-PT-5a execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool irma4mcc-structural"

echo " Input is DLCshifumi-PT-5a, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r067-smll-152649739700200"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;