About the Execution of Irma.struct for DLCround-PT-06a

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 697.570 | 15831.00 | 26070.00 | 821.70 | F | normal |

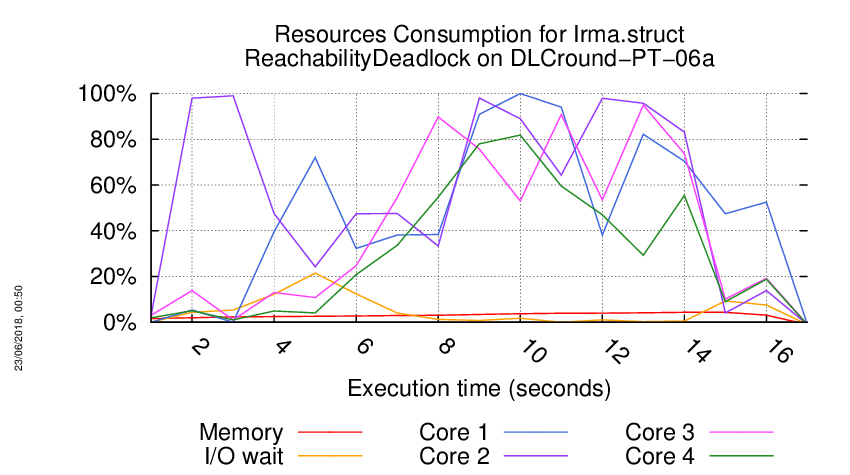

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

.......................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................

/home/mcc/execution

total 500K

-rw-r--r-- 1 mcc users 3.9K May 15 18:54 CTLCardinality.txt

-rw-r--r-- 1 mcc users 23K May 15 18:54 CTLCardinality.xml

-rw-r--r-- 1 mcc users 2.7K May 15 18:54 CTLFireability.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 CTLFireability.xml

-rw-r--r-- 1 mcc users 4.0K May 15 18:50 GenericPropertiesDefinition.xml

-rw-r--r-- 1 mcc users 5.9K May 15 18:50 GenericPropertiesVerdict.xml

-rw-r--r-- 1 mcc users 2.2K May 15 18:54 LTLCardinality.txt

-rw-r--r-- 1 mcc users 9.0K May 15 18:54 LTLCardinality.xml

-rw-r--r-- 1 mcc users 1.8K May 15 18:54 LTLFireability.txt

-rw-r--r-- 1 mcc users 8.2K May 15 18:54 LTLFireability.xml

-rw-r--r-- 1 mcc users 3.6K May 15 18:54 ReachabilityCardinality.txt

-rw-r--r-- 1 mcc users 19K May 15 18:54 ReachabilityCardinality.xml

-rw-r--r-- 1 mcc users 106 May 15 18:54 ReachabilityDeadlock.txt

-rw-r--r-- 1 mcc users 344 May 15 18:54 ReachabilityDeadlock.xml

-rw-r--r-- 1 mcc users 2.8K May 15 18:54 ReachabilityFireability.txt

-rw-r--r-- 1 mcc users 17K May 15 18:54 ReachabilityFireability.xml

-rw-r--r-- 1 mcc users 1.6K May 15 18:54 UpperBounds.txt

-rw-r--r-- 1 mcc users 3.6K May 15 18:54 UpperBounds.xml

-rw-r--r-- 1 mcc users 6 May 15 18:50 equiv_col

-rw-r--r-- 1 mcc users 4 May 15 18:50 instance

-rw-r--r-- 1 mcc users 6 May 15 18:50 iscolored

-rw-r--r-- 1 mcc users 325K May 15 18:50 model.pnml

=====================================================================

Generated by BenchKit 2-3637

Executing tool irma4mcc-structural

Input is DLCround-PT-06a, examination is ReachabilityDeadlock

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r067-smll-152649739500048

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME DLCround-PT-06a-ReachabilityDeadlock-0

=== Now, execution of the tool begins

BK_START 1526623928656

BK_STOP 1526623944487

--------------------

content from stderr:

Prefix is 75f5f979.

Reading known information in /usr/share/mcc4mcc/75f5f979-known.json.

Reading learned information in /usr/share/mcc4mcc/75f5f979-learned.json.

Reading value translations in /usr/share/mcc4mcc/75f5f979-values.json.

Using directory /home/mcc/execution for input, as it contains a model.pnml file.

Using DLCround-PT-06a as instance name.

Using DLCround as model name.

Using algorithm or tool decision-tree.

Model characteristics are: {'Examination': 'ReachabilityDeadlock', 'Place/Transition': True, 'Colored': False, 'Relative-Time': 1, 'Relative-Memory': 1, 'Ordinary': True, 'Simple Free Choice': False, 'Extended Free Choice': False, 'State Machine': False, 'Marked Graph': False, 'Connected': True, 'Strongly Connected': False, 'Source Place': True, 'Sink Place': False, 'Source Transition': False, 'Sink Transition': False, 'Loop Free': None, 'Conservative': False, 'Sub-Conservative': False, 'Nested Units': True, 'Safe': True, 'Deadlock': None, 'Reversible': None, 'Quasi Live': None, 'Live': None}.

Known tools are: [{'Time': 3575, 'Memory': 300.67, 'Tool': 'itstools'}, {'Time': 14807, 'Memory': 2210.21, 'Tool': 'marcie'}, {'Time': 35088, 'Memory': 864.85, 'Tool': 'gspn'}].

Learned tools are: [{'Tool': 'lola'}].

ReachabilityDeadlock itstools DLCround-PT-06a...

May 18, 2018 6:12:19 AM fr.lip6.move.gal.application.Application start

INFO: Running its-tools with arguments : [-z3path, /usr/bin/z3, -yices2path, /usr/bin/yices, -ltsminpath, /usr/bin, -smt, -its, -pnfolder, /mcc-data, -examination, ReachabilityDeadlock]

May 18, 2018 6:12:19 AM fr.lip6.move.gal.application.MccTranslator transformPNML

INFO: Parsing pnml file : /mcc-data/model.pnml

May 18, 2018 6:12:19 AM fr.lip6.move.gal.nupn.PTNetReader loadFromXML

INFO: Load time of PNML (sax parser for PT used): 181 ms

May 18, 2018 6:12:19 AM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 197 places.

May 18, 2018 6:12:20 AM fr.lip6.move.gal.pnml.togal.PTGALTransformer handlePage

INFO: Transformed 1313 transitions.

May 18, 2018 6:12:20 AM fr.lip6.move.gal.pnml.togal.PnmlToGalTransformer transform

INFO: Found NUPN structural information;

May 18, 2018 6:12:20 AM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /mcc-data/model.pnml.img.gal : 79 ms

May 18, 2018 6:12:20 AM fr.lip6.move.gal.instantiate.GALRewriter flatten

INFO: Flatten gal took : 567 ms

Flatten gal took : 576 ms

May 18, 2018 6:12:20 AM fr.lip6.move.serialization.SerializationUtil systemToFile

INFO: Time to serialize gal into /mcc-data/model.pnml.simple.gal : 9 ms

May 18, 2018 6:12:21 AM fr.lip6.move.gal.semantics.DeterministicNextBuilder getDeterministicNext

INFO: Input system was already deterministic with 1313 transitions.

Constant places removed 1 places and 1 transitions.

Reduce isomorphic transitions removed 135 transitions.

Performed 4 Post agglomeration using F-continuation condition.

Iterating post reduction 0 with 140 rules applied. Total rules applied 140 place count 196 transition count 1173

Constant places removed 102 places and 0 transitions.

Reduce isomorphic transitions removed 967 transitions.

Performed 18 Post agglomeration using F-continuation condition.

Iterating post reduction 1 with 1087 rules applied. Total rules applied 1227 place count 94 transition count 188

Constant places removed 18 places and 0 transitions.

Reduce isomorphic transitions removed 11 transitions.

Iterating post reduction 2 with 29 rules applied. Total rules applied 1256 place count 76 transition count 177

Performed 11 Post agglomeration using F-continuation condition.

Constant places removed 11 places and 0 transitions.

Reduce isomorphic transitions removed 7 transitions.

Iterating post reduction 3 with 18 rules applied. Total rules applied 1274 place count 65 transition count 159

Performed 7 Post agglomeration using F-continuation condition.

Constant places removed 7 places and 0 transitions.

Reduce isomorphic transitions removed 7 transitions.

Iterating post reduction 4 with 14 rules applied. Total rules applied 1288 place count 58 transition count 159

Applied a total of 1288 rules in 67 ms. Remains 58 /197 variables (removed 139) and now considering 159/1313 (removed 1154) transitions.

Normalized transition count is 102

// Phase 1: matrix 102 rows 58 cols

FORMULA DLCround-PT-06a-ReachabilityDeadlock-0 FALSE TECHNIQUES TOPOLOGICAL SAT_SMT STRUCTURAL_REDUCTION

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="DLCround-PT-06a"

export BK_EXAMINATION="ReachabilityDeadlock"

export BK_TOOL="irma4mcc-structural"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/DLCround-PT-06a.tgz

mv DLCround-PT-06a execution

cd execution

pwd

ls -lh

# this is for BenchKit: explicit launching of the test

echo "====================================================================="

echo " Generated by BenchKit 2-3637"

echo " Executing tool irma4mcc-structural"

echo " Input is DLCround-PT-06a, examination is ReachabilityDeadlock"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r067-smll-152649739500048"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityDeadlock" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityDeadlock" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityDeadlock.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityDeadlock.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityDeadlock.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;