About the Execution of MARCIE for PermAdmissibility-COL-01

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 9809.690 | 236171.00 | 236019.00 | 20.20 | TTFTFFTFFTTTFTTT | normal |

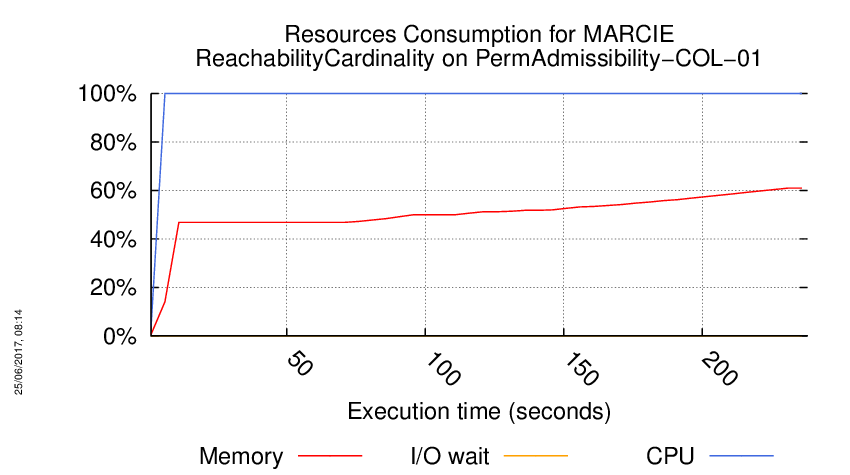

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

.......

=====================================================================

Generated by BenchKit 2-3254

Executing tool marcie

Input is PermAdmissibility-COL-01, examination is ReachabilityCardinality

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 1

Run identifier is r031-blw7-149440474100349

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-0

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-1

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-10

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-11

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-12

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-13

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-14

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-15

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-2

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-3

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-4

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-5

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-6

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-7

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-8

FORMULA_NAME PermAdmissibility-COL-01-ReachabilityCardinality-9

=== Now, execution of the tool begins

BK_START 1494463287791

timeout --kill-after=10s --signal=SIGINT 1m for testing only

Marcie rev. 8852M (built: crohr on 2017-05-03)

A model checker for Generalized Stochastic Petri nets

authors: Alex Tovchigrechko (IDD package and CTL model checking)

Martin Schwarick (Symbolic numerical analysis and CSL model checking)

Christian Rohr (Simulative and approximative numerical model checking)

marcie@informatik.tu-cottbus.de

called as: marcie --net-file=model.pnml --mcc-file=ReachabilityCardinality.xml --memory=6

parse successfull

net created successfully

Unfolding complete |P|=208|T|=1024|A|=6080

Time for unfolding: 0m 2.487sec

Net: PermAdmissibility_COL_01

(NrP: 208 NrTr: 1024 NrArc: 5984)

parse formulas

formulas created successfully

place and transition orderings generation:0m 0.022sec

net check time: 0m 0.001sec

init dd package: 0m 1.122sec

parse successfull

net created successfully

Unfolding complete |P|=208|T|=1024|A|=6080

Time for unfolding: 0m 2.410sec

Net: PermAdmissibility_COL_01

(NrP: 208 NrTr: 1024 NrArc: 5984)

parse formulas

formulas created successfully

place and transition orderings generation:0m 0.024sec

net check time: 0m 0.002sec

init dd package: 0m 3.631sec

RS generation: 0m42.792sec

-> reachability set: #nodes 53950 (5.4e+04) #states 52,537 (4)

starting MCC model checker

--------------------------

checking: EF [~ [~ [1<=c19_dot]]]

normalized: E [true U 1<=c19_dot]

abstracting: (1<=c19_dot)

states: 4,672 (3)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-1 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m55.537sec

checking: EF [3<=c5_dot]

normalized: E [true U 3<=c5_dot]

abstracting: (3<=c5_dot)

states: 0

-> the formula is FALSE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-2 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.035sec

checking: EF [[3<=c8_dot & 1<=c13_dot]]

normalized: E [true U [3<=c8_dot & 1<=c13_dot]]

abstracting: (1<=c13_dot)

states: 256

abstracting: (3<=c8_dot)

states: 0

-> the formula is FALSE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-15 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.068sec

checking: EF [~ [c18_dot<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)]]

normalized: E [true U ~ [c18_dot<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)]]

abstracting: (c18_dot<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0))

states: 47,865 (4)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-3 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m10.092sec

checking: AG [~ [~ [sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0)<=sum(aux14_input7, aux14_input6, aux14_input5, aux14_input4, aux14_input3, aux14_input2, aux14_input1, aux14_input0)]]]

normalized: ~ [E [true U ~ [sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0)<=sum(aux14_input7, aux14_input6, aux14_input5, aux14_input4, aux14_input3, aux14_input2, aux14_input1, aux14_input0)]]]

abstracting: (sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0)<=sum(aux14_input7, aux14_input6, aux14_input5, aux14_input4, aux14_input3, aux14_input2, aux14_input1, aux14_input0))

states: 52,537 (4)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-0 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.131sec

checking: AG [sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)<=sum(aux10_input7, aux10_input6, aux10_input5, aux10_input4, aux10_input3, aux10_input2, aux10_input1, aux10_input0)]

normalized: ~ [E [true U ~ [sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)<=sum(aux10_input7, aux10_input6, aux10_input5, aux10_input4, aux10_input3, aux10_input2, aux10_input1, aux10_input0)]]]

abstracting: (sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)<=sum(aux10_input7, aux10_input6, aux10_input5, aux10_input4, aux10_input3, aux10_input2, aux10_input1, aux10_input0))

states: 10,489 (4)

-> the formula is FALSE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-6 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m24.763sec

checking: AG [~ [[2<=c19_dot & [1<=sum(in4_input7, in4_input6, in4_input5, in4_input4, in4_input3, in4_input2, in4_input1, in4_input0) | 1<=sum(out2_input7, out2_input6, out2_input5, out2_input4, out2_input3, out2_input2, out2_input1, out2_input0)]]]]

normalized: ~ [E [true U [2<=c19_dot & [1<=sum(in4_input7, in4_input6, in4_input5, in4_input4, in4_input3, in4_input2, in4_input1, in4_input0) | 1<=sum(out2_input7, out2_input6, out2_input5, out2_input4, out2_input3, out2_input2, out2_input1, out2_input0)]]]]

abstracting: (1<=sum(out2_input7, out2_input6, out2_input5, out2_input4, out2_input3, out2_input2, out2_input1, out2_input0))

states: 46,720 (4)

abstracting: (1<=sum(in4_input7, in4_input6, in4_input5, in4_input4, in4_input3, in4_input2, in4_input1, in4_input0))

states: 25

abstracting: (2<=c19_dot)

states: 0

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-4 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.144sec

checking: EF [~ [[[3<=c16_dot & 2<=sum(aux13_input7, aux13_input6, aux13_input5, aux13_input4, aux13_input3, aux13_input2, aux13_input1, aux13_input0)] | ~ [2<=sum(out1_input7, out1_input6, out1_input5, out1_input4, out1_input3, out1_input2, out1_input1, out1_input0)]]]]

normalized: E [true U ~ [[[3<=c16_dot & 2<=sum(aux13_input7, aux13_input6, aux13_input5, aux13_input4, aux13_input3, aux13_input2, aux13_input1, aux13_input0)] | ~ [2<=sum(out1_input7, out1_input6, out1_input5, out1_input4, out1_input3, out1_input2, out1_input1, out1_input0)]]]]

abstracting: (2<=sum(out1_input7, out1_input6, out1_input5, out1_input4, out1_input3, out1_input2, out1_input1, out1_input0))

states: 0

abstracting: (2<=sum(aux13_input7, aux13_input6, aux13_input5, aux13_input4, aux13_input3, aux13_input2, aux13_input1, aux13_input0))

states: 5,136 (3)

abstracting: (3<=c16_dot)

states: 0

-> the formula is FALSE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-10 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.159sec

checking: AG [~ [[[c18_dot<=c15_dot & 2<=c19_dot] & [sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0)<=c11_dot & 1<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)]]]]

normalized: ~ [E [true U [[sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0)<=c11_dot & 1<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)] & [c18_dot<=c15_dot & 2<=c19_dot]]]]

abstracting: (2<=c19_dot)

states: 0

abstracting: (c18_dot<=c15_dot)

states: 47,865 (4)

abstracting: (1<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0))

states: 42,048 (4)

abstracting: (sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0)<=c11_dot)

states: 51,001 (4)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-7 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.205sec

checking: AG [[[c9_dot<=c17_dot | [c11_dot<=sum(aux11_input7, aux11_input6, aux11_input5, aux11_input4, aux11_input3, aux11_input2, aux11_input1, aux11_input0) | 2<=sum(out5_input7, out5_input6, out5_input5, out5_input4, out5_input3, out5_input2, out5_input1, out5_input0)]] | 3<=c5_dot]]

normalized: ~ [E [true U ~ [[3<=c5_dot | [c9_dot<=c17_dot | [c11_dot<=sum(aux11_input7, aux11_input6, aux11_input5, aux11_input4, aux11_input3, aux11_input2, aux11_input1, aux11_input0) | 2<=sum(out5_input7, out5_input6, out5_input5, out5_input4, out5_input3, out5_input2, out5_input1, out5_input0)]]]]]]

abstracting: (2<=sum(out5_input7, out5_input6, out5_input5, out5_input4, out5_input3, out5_input2, out5_input1, out5_input0))

states: 0

abstracting: (c11_dot<=sum(aux11_input7, aux11_input6, aux11_input5, aux11_input4, aux11_input3, aux11_input2, aux11_input1, aux11_input0))

states: 52,473 (4)

abstracting: (c9_dot<=c17_dot)

states: 52,521 (4)

abstracting: (3<=c5_dot)

states: 0

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-9 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.216sec

checking: AG [[c17_dot<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0) & [~ [2<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)] | 1<=sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0)]]]

normalized: ~ [E [true U ~ [[c17_dot<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0) & [1<=sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0) | ~ [2<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0)]]]]]]

abstracting: (2<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0))

states: 0

abstracting: (1<=sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0))

states: 29,200 (4)

abstracting: (c17_dot<=sum(out4_input7, out4_input6, out4_input5, out4_input4, out4_input3, out4_input2, out4_input1, out4_input0))

states: 51,369 (4)

-> the formula is FALSE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-13 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 8.867sec

checking: AG [~ [[3<=sum(out5_input7, out5_input6, out5_input5, out5_input4, out5_input3, out5_input2, out5_input1, out5_input0) & [c20_dot<=sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0) & sum(aux11_input7, aux11_input6, aux11_input5, aux11_input4, aux11_input3, aux11_input2, aux11_input1, aux11_input0)<=sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)]]]]

normalized: ~ [E [true U [3<=sum(out5_input7, out5_input6, out5_input5, out5_input4, out5_input3, out5_input2, out5_input1, out5_input0) & [c20_dot<=sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0) & sum(aux11_input7, aux11_input6, aux11_input5, aux11_input4, aux11_input3, aux11_input2, aux11_input1, aux11_input0)<=sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)]]]]

abstracting: (sum(aux11_input7, aux11_input6, aux11_input5, aux11_input4, aux11_input3, aux11_input2, aux11_input1, aux11_input0)<=sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0))

states: 52,281 (4)

abstracting: (c20_dot<=sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0))

states: 52,537 (4)

abstracting: (3<=sum(out5_input7, out5_input6, out5_input5, out5_input4, out5_input3, out5_input2, out5_input1, out5_input0))

states: 0

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-5 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.204sec

checking: EF [[1<=c20_dot & [[sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)<=sum(aux13_input7, aux13_input6, aux13_input5, aux13_input4, aux13_input3, aux13_input2, aux13_input1, aux13_input0) | c12_dot<=sum(aux8_input7, aux8_input6, aux8_input5, aux8_input4, aux8_input3, aux8_input2, aux8_input1, aux8_input0)] & ~ [2<=sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)]]]]

normalized: E [true U [1<=c20_dot & [~ [2<=sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)] & [sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)<=sum(aux13_input7, aux13_input6, aux13_input5, aux13_input4, aux13_input3, aux13_input2, aux13_input1, aux13_input0) | c12_dot<=sum(aux8_input7, aux8_input6, aux8_input5, aux8_input4, aux8_input3, aux8_input2, aux8_input1, aux8_input0)]]]]

abstracting: (c12_dot<=sum(aux8_input7, aux8_input6, aux8_input5, aux8_input4, aux8_input3, aux8_input2, aux8_input1, aux8_input0))

states: 52,537 (4)

abstracting: (sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)<=sum(aux13_input7, aux13_input6, aux13_input5, aux13_input4, aux13_input3, aux13_input2, aux13_input1, aux13_input0))

states: 52,537 (4)

abstracting: (2<=sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0))

states: 3,504 (3)

abstracting: (1<=c20_dot)

states: 18,688 (4)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-14 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 1m16.583sec

checking: AG [~ [[sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)<=sum(out2_input7, out2_input6, out2_input5, out2_input4, out2_input3, out2_input2, out2_input1, out2_input0) & [sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)<=sum(aux10_input7, aux10_input6, aux10_input5, aux10_input4, aux10_input3, aux10_input2, aux10_input1, aux10_input0) & 2<=sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)]]]]

normalized: ~ [E [true U [sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)<=sum(out2_input7, out2_input6, out2_input5, out2_input4, out2_input3, out2_input2, out2_input1, out2_input0) & [sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)<=sum(aux10_input7, aux10_input6, aux10_input5, aux10_input4, aux10_input3, aux10_input2, aux10_input1, aux10_input0) & 2<=sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)]]]]

abstracting: (2<=sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0))

states: 1

abstracting: (sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)<=sum(aux10_input7, aux10_input6, aux10_input5, aux10_input4, aux10_input3, aux10_input2, aux10_input1, aux10_input0))

states: 52,532 (4)

abstracting: (sum(aux15_input7, aux15_input6, aux15_input5, aux15_input4, aux15_input3, aux15_input2, aux15_input1, aux15_input0)<=sum(out2_input7, out2_input6, out2_input5, out2_input4, out2_input3, out2_input2, out2_input1, out2_input0))

states: 49,033 (4)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-8 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.312sec

checking: EF [[[~ [sum(out8_input7, out8_input6, out8_input5, out8_input4, out8_input3, out8_input2, out8_input1, out8_input0)<=sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0)] | ~ [1<=sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0)]] & [[3<=c15_dot | sum(in2_input7, in2_input6, in2_input5, in2_input4, in2_input3, in2_input2, in2_input1, in2_input0)<=sum(aux14_input7, aux14_input6, aux14_input5, aux14_input4, aux14_input3, aux14_input2, aux14_input1, aux14_input0)] & ~ [sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)<=c11_dot]]]]

normalized: E [true U [[~ [sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)<=c11_dot] & [3<=c15_dot | sum(in2_input7, in2_input6, in2_input5, in2_input4, in2_input3, in2_input2, in2_input1, in2_input0)<=sum(aux14_input7, aux14_input6, aux14_input5, aux14_input4, aux14_input3, aux14_input2, aux14_input1, aux14_input0)]] & [~ [1<=sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0)] | ~ [sum(out8_input7, out8_input6, out8_input5, out8_input4, out8_input3, out8_input2, out8_input1, out8_input0)<=sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0)]]]]

abstracting: (sum(out8_input7, out8_input6, out8_input5, out8_input4, out8_input3, out8_input2, out8_input1, out8_input0)<=sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0))

states: 33,849 (4)

abstracting: (1<=sum(aux16_input7, aux16_input6, aux16_input5, aux16_input4, aux16_input3, aux16_input2, aux16_input1, aux16_input0))

states: 29,200 (4)

abstracting: (sum(in2_input7, in2_input6, in2_input5, in2_input4, in2_input3, in2_input2, in2_input1, in2_input0)<=sum(aux14_input7, aux14_input6, aux14_input5, aux14_input4, aux14_input3, aux14_input2, aux14_input1, aux14_input0))

states: 52,512 (4)

abstracting: (3<=c15_dot)

states: 0

abstracting: (sum(in1_input7, in1_input6, in1_input5, in1_input4, in1_input3, in1_input2, in1_input1, in1_input0)<=c11_dot)

states: 52,532 (4)

-> the formula is FALSE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-12 FALSE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.379sec

checking: AG [[[[3<=sum(aux7_input7, aux7_input6, aux7_input5, aux7_input4, aux7_input3, aux7_input2, aux7_input1, aux7_input0) & sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0)<=sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0)] | [2<=sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0) | c14_dot<=sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)]] | [[sum(out1_input7, out1_input6, out1_input5, out1_input4, out1_input3, out1_input2, out1_input1, out1_input0)<=sum(aux8_input7, aux8_input6, aux8_input5, aux8_input4, aux8_input3, aux8_input2, aux8_input1, aux8_input0) | sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)<=c11_dot] | [c8_dot<=sum(out7_input7, out7_input6, out7_input5, out7_input4, out7_input3, out7_input2, out7_input1, out7_input0) & 1<=c9_dot]]]]

normalized: ~ [E [true U ~ [[[[sum(out1_input7, out1_input6, out1_input5, out1_input4, out1_input3, out1_input2, out1_input1, out1_input0)<=sum(aux8_input7, aux8_input6, aux8_input5, aux8_input4, aux8_input3, aux8_input2, aux8_input1, aux8_input0) | sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)<=c11_dot] | [c8_dot<=sum(out7_input7, out7_input6, out7_input5, out7_input4, out7_input3, out7_input2, out7_input1, out7_input0) & 1<=c9_dot]] | [[2<=sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0) | c14_dot<=sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)] | [3<=sum(aux7_input7, aux7_input6, aux7_input5, aux7_input4, aux7_input3, aux7_input2, aux7_input1, aux7_input0) & sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0)<=sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0)]]]]]]

abstracting: (sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0)<=sum(out6_input7, out6_input6, out6_input5, out6_input4, out6_input3, out6_input2, out6_input1, out6_input0))

states: 52,537 (4)

abstracting: (3<=sum(aux7_input7, aux7_input6, aux7_input5, aux7_input4, aux7_input3, aux7_input2, aux7_input1, aux7_input0))

states: 0

abstracting: (c14_dot<=sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0))

states: 52,537 (4)

abstracting: (2<=sum(aux9_input7, aux9_input6, aux9_input5, aux9_input4, aux9_input3, aux9_input2, aux9_input1, aux9_input0))

states: 640

abstracting: (1<=c9_dot)

states: 16

abstracting: (c8_dot<=sum(out7_input7, out7_input6, out7_input5, out7_input4, out7_input3, out7_input2, out7_input1, out7_input0))

states: 52,521 (4)

abstracting: (sum(aux12_input7, aux12_input6, aux12_input5, aux12_input4, aux12_input3, aux12_input2, aux12_input1, aux12_input0)<=c11_dot)

states: 48,313 (4)

abstracting: (sum(out1_input7, out1_input6, out1_input5, out1_input4, out1_input3, out1_input2, out1_input1, out1_input0)<=sum(aux8_input7, aux8_input6, aux8_input5, aux8_input4, aux8_input3, aux8_input2, aux8_input1, aux8_input0))

states: 5,817 (3)

-> the formula is TRUE

FORMULA PermAdmissibility-COL-01-ReachabilityCardinality-11 TRUE TECHNIQUES SEQUENTIAL_PROCESSING DECISION_DIAGRAMS UNFOLDING_TO_PT

MC time: 0m 0.551sec

totally nodes used: 35369141 (3.5e+07)

number of garbage collections: 0

fire ops cache: hits/miss/sum: 55908278 288735771 344644049

used/not used/entry size/cache size: 66445797 663067 16 1024MB

basic ops cache: hits/miss/sum: 7694227 37151798 44846025

used/not used/entry size/cache size: 16531756 245460 12 192MB

unary ops cache: hits/miss/sum: 0 0 0

used/not used/entry size/cache size: 0 16777216 8 128MB

abstract ops cache: hits/miss/sum: 0 435008 435008

used/not used/entry size/cache size: 1 16777215 12 192MB

state nr cache: hits/miss/sum: 9829 57808 67637

used/not used/entry size/cache size: 57698 8330910 32 256MB

max state cache: hits/miss/sum: 0 0 0

used/not used/entry size/cache size: 0 8388608 32 256MB

uniqueHash elements/entry size/size: 67108864 4 256MB

0 42417446

1 16550132

2 6102165

3 1625978

4 341841

5 60284

6 9559

7 1303

8 142

9 14

>= 10 0

Total processing time: 3m56.003sec

BK_STOP 1494463523962

--------------------

content from stderr:

check for maximal unmarked siphon

found

The net has a maximal unmarked siphon:

aux5_input7

aux5_input6

in3_input3

aux5_input3

aux5_input2

in1_input2

aux7_input5

in3_input1

in3_input2

aux7_input4

aux6_input7

aux6_input6

aux8_input5

aux8_input1

aux8_input4

aux8_input0

aux6_input3

aux7_input1

aux6_input2

aux7_input0

in3_input6

in3_input7

in4_input0

in4_input1

in4_input2

in4_input3

in4_input4

in4_input5

in1_input3

in1_input4

in1_input5

in1_input6

in1_input7

in2_input0

in2_input1

in2_input4

in2_input5

in2_input6

in2_input7

in3_input0

The net has transition(s) that can never fire:

switch1_0_2

switch1_0_3

switch1_0_6

switch1_0_7

switch1_1_0

switch3_3_0

switch3_3_1

switch3_3_2

switch3_3_3

switch3_4_7

switch3_5_0

switch3_5_2

switch3_5_1

switch1_0_0

switch1_0_1

switch5_0_4

switch5_0_5

switch5_1_0

switch5_1_1

switch5_1_4

switch5_1_5

switch1_1_1

switch1_1_2

switch1_1_3

switch1_1_6

switch1_1_7

switch1_2_0

switch1_2_1

switch1_2_2

switch1_2_3

switch1_2_4

switch1_2_5

switch1_2_6

switch1_2_7

switch1_3_0

switch1_3_1

switch1_3_2

switch1_3_3

switch1_3_4

switch1_3_5

switch1_3_6

switch1_3_7

switch1_4_0

switch1_4_1

switch1_4_2

switch1_4_3

switch1_4_4

switch1_4_5

switch1_4_6

switch1_4_7

switch1_5_0

switch1_5_1

switch1_5_2

switch1_5_3

switch1_5_4

switch1_5_5

switch1_5_6

switch1_5_7

switch1_6_0

switch1_6_1

switch1_6_2

switch1_6_3

switch1_6_4

switch1_6_5

switch1_6_6

switch1_6_7

switch1_7_0

switch1_7_1

switch1_7_2

switch1_7_3

switch1_7_4

switch1_7_5

switch1_7_6

switch1_7_7

switch3_0_0

switch3_0_1

switch3_0_2

switch3_0_3

switch3_0_4

switch3_0_5

switch3_0_6

switch3_0_7

switch3_1_0

switch3_1_1

switch3_1_2

switch3_1_3

switch3_1_4

switch3_1_5

switch3_1_6

switch3_1_7

switch3_2_0

switch3_2_1

switch3_2_2

switch3_2_3

switch3_2_4

switch3_2_5

switch6_5_5

switch6_6_0

switch6_6_1

switch6_6_2

switch6_6_3

switch6_6_4

switch3_3_4

switch3_3_5

switch3_4_0

switch3_4_1

switch3_4_2

switch3_4_3

switch3_4_4

switch3_4_5

switch3_4_6

switch7_1_4

switch7_1_5

switch7_2_0

switch7_2_1

switch3_5_3

switch3_5_4

switch3_5_5

switch3_5_6

switch3_5_7

switch3_6_0

switch3_6_1

switch3_6_2

switch3_6_3

switch3_6_4

switch3_6_5

switch3_6_6

switch3_6_7

switch3_7_0

switch3_7_1

switch3_7_2

switch3_7_3

switch3_7_4

switch3_7_5

switch3_7_6

switch3_7_7

switch2_0_0

switch2_0_1

switch2_0_2

switch2_0_3

switch2_0_6

switch2_0_7

switch2_1_0

switch2_1_1

switch2_1_2

switch2_1_3

switch2_1_6

switch2_1_7

switch2_2_0

switch2_2_1

switch2_2_2

switch2_2_3

switch2_2_4

switch2_2_5

switch2_2_6

switch2_2_7

switch2_3_0

switch2_3_1

switch2_3_2

switch2_3_3

switch2_3_4

switch2_3_5

switch2_3_6

switch2_3_7

switch2_4_0

switch2_4_1

switch2_4_2

switch2_4_3

switch2_4_4

switch2_4_5

switch2_4_6

switch2_4_7

switch2_5_0

switch2_5_1

switch2_5_2

switch2_5_3

switch2_5_4

switch2_5_5

switch2_5_6

switch2_5_7

switch2_6_0

switch2_6_1

switch2_6_2

switch2_6_3

switch2_6_4

switch2_6_5

switch2_6_6

switch2_6_7

switch2_7_0

switch2_7_1

switch2_7_2

switch2_7_3

switch2_7_4

switch2_7_5

switch2_7_6

switch2_7_7

switch4_0_0

switch4_0_1

switch4_0_2

switch4_0_3

switch4_0_4

switch4_0_5

switch4_0_6

switch4_0_7

switch4_1_0

switch4_1_1

switch4_1_2

switch4_1_3

switch4_1_4

switch4_1_5

switch4_1_6

switch4_1_7

switch4_2_0

switch4_2_1

switch4_2_2

switch4_2_3

switch4_2_4

switch4_2_5

switch4_3_0

switch4_3_1

switch4_3_2

switch4_3_3

switch4_3_4

switch4_3_5

switch4_4_0

switch4_4_1

switch4_4_2

switch4_4_3

switch4_4_4

switch4_4_5

switch4_4_6

switch4_4_7

switch4_5_0

switch4_5_1

switch4_5_2

switch4_5_3

switch4_5_4

switch4_5_5

switch4_5_6

switch4_5_7

switch4_6_0

switch4_6_1

switch4_6_2

switch4_6_3

switch4_6_4

switch4_6_5

switch4_6_6

switch4_6_7

switch4_7_0

switch4_7_1

switch4_7_2

switch4_7_3

switch4_7_4

switch4_7_5

switch4_7_6

switch4_7_7

switch5_0_0

switch5_0_1

switch5_2_0

switch5_2_1

switch5_2_2

switch5_2_3

switch5_2_4

switch5_2_5

switch5_2_6

switch5_2_7

switch5_3_0

switch5_3_1

switch5_3_2

switch5_3_3

switch5_3_4

switch5_3_5

switch5_3_6

switch5_3_7

switch5_4_0

switch5_4_1

switch5_4_4

switch5_4_5

switch5_5_0

switch5_5_1

switch5_5_4

switch5_5_5

switch5_6_0

switch5_6_1

switch5_6_2

switch5_6_3

switch5_6_4

switch5_6_5

switch5_6_6

switch5_6_7

switch5_7_0

switch5_7_1

switch5_7_2

switch5_7_3

switch5_7_4

switch5_7_5

switch5_7_6

switch5_7_7

switch8_0_0

switch8_0_1

switch8_0_4

switch8_0_5

switch8_1_0

switch8_1_1

switch8_1_4

switch8_1_5

switch8_2_0

switch8_2_1

switch8_2_2

switch8_2_3

switch8_2_4

switch8_2_5

switch8_2_6

switch8_2_7

switch8_3_0

switch8_3_1

switch8_3_2

switch8_3_3

switch8_3_4

switch8_3_5

switch8_3_6

switch8_3_7

switch8_4_0

switch8_4_1

switch8_4_4

switch8_4_5

switch8_5_0

switch8_5_1

switch8_5_4

switch8_5_5

switch8_6_0

switch8_6_1

switch8_6_2

switch8_6_3

switch8_6_4

switch8_6_5

switch8_6_6

switch8_6_7

switch8_7_0

switch8_7_1

switch8_7_2

switch8_7_3

switch8_7_4

switch8_7_5

switch8_7_6

switch8_7_7

switch6_0_0

switch6_0_1

switch6_0_4

switch6_0_5

switch6_1_0

switch6_1_1

switch6_1_4

switch6_1_5

switch6_2_0

switch6_2_1

switch6_2_2

switch6_2_3

switch6_2_4

switch6_2_5

switch6_2_6

switch6_2_7

switch6_3_0

switch6_3_1

switch6_3_2

switch6_3_3

switch6_3_4

switch6_3_5

switch6_3_6

switch6_3_7

switch6_4_0

switch6_4_1

switch6_4_4

switch6_4_5

switch6_5_0

switch6_5_1

switch6_5_4

switch6_6_5

switch6_6_6

switch6_6_7

switch6_7_0

switch6_7_1

switch6_7_2

switch6_7_3

switch6_7_4

switch6_7_5

switch6_7_6

switch6_7_7

switch7_0_0

switch7_0_1

switch7_0_4

switch7_0_5

switch7_1_0

switch7_1_1

switch7_2_2

switch7_2_3

switch7_2_4

switch7_2_5

switch7_2_6

switch7_2_7

switch7_3_0

switch7_3_1

switch7_3_2

switch7_3_3

switch7_3_4

switch7_3_5

switch7_3_6

switch7_3_7

switch7_4_0

switch7_4_1

switch7_4_4

switch7_4_5

switch7_5_0

switch7_5_1

switch7_5_4

switch7_5_5

switch7_6_0

switch7_6_1

switch7_6_2

switch7_6_3

switch7_6_4

switch7_6_5

switch7_6_6

switch7_6_7

switch7_7_0

switch7_7_1

switch7_7_2

switch7_7_3

switch7_7_4

switch7_7_5

switch7_7_6

switch7_7_7

check for constant places

ok

check if there are places and transitions

ok

check if there are transitions without pre-places

ok

check if at least one transition is enabled in m0

ok

check if there are transitions that can never fire

ok

ptnet_zbdd.cc:66: Boundedness exception: net maybe not 1-bounded!

check for maximal unmarked siphon

found

The net has a maximal unmarked siphon:

aux5_input3

aux5_input2

aux5_input7

aux5_input6

aux7_input5

in1_input2

aux7_input0

aux6_input2

aux6_input7

aux6_input3

aux7_input1

aux8_input5

aux8_input4

aux8_input1

aux8_input0

in3_input2

in3_input3

aux6_input6

aux7_input4

in2_input1

in2_input4

in2_input5

in2_input6

in2_input7

in3_input0

in3_input1

in1_input3

in1_input4

in1_input5

in1_input6

in1_input7

in2_input0

in3_input6

in3_input7

in4_input0

in4_input1

in4_input2

in4_input3

in4_input4

in4_input5

The net has transition(s) that can never fire:

switch1_0_0

switch1_0_1

switch5_0_4

switch5_0_5

switch5_1_0

switch5_1_1

switch5_1_4

switch5_1_5

switch1_1_1

switch1_1_2

switch1_1_3

switch1_1_6

switch1_1_7

switch1_2_0

switch1_2_1

switch1_2_2

switch1_2_3

switch1_2_4

switch1_2_5

switch1_2_6

switch1_2_7

switch1_3_0

switch1_3_1

switch1_3_2

switch1_3_3

switch1_3_4

switch1_3_5

switch1_3_6

switch1_3_7

switch1_4_0

switch1_4_1

switch1_4_2

switch1_4_3

switch1_4_4

switch1_4_5

switch1_4_6

switch1_4_7

switch1_5_0

switch1_5_1

switch1_5_2

switch1_5_3

switch1_5_4

switch1_5_5

switch1_5_6

switch1_5_7

switch1_0_2

switch1_0_3

switch1_0_6

switch1_0_7

switch1_1_0

switch3_3_0

switch3_3_1

switch3_3_2

switch3_3_3

switch1_6_0

switch1_6_1

switch1_6_2

switch1_6_3

switch1_6_4

switch1_6_5

switch1_6_6

switch1_6_7

switch1_7_0

switch1_7_1

switch1_7_2

switch1_7_3

switch1_7_4

switch1_7_5

switch1_7_6

switch1_7_7

switch3_0_0

switch3_0_1

switch3_0_2

switch3_0_3

switch3_0_4

switch3_0_5

switch3_0_6

switch3_0_7

switch3_1_0

switch3_1_1

switch3_1_2

switch3_1_3

switch3_1_4

switch3_1_5

switch3_1_6

switch3_1_7

switch3_2_0

switch3_2_1

switch3_2_2

switch3_2_3

switch3_2_4

switch3_2_5

switch6_5_5

switch6_6_0

switch6_6_1

switch6_6_2

switch6_6_3

switch6_6_4

switch3_3_4

switch3_3_5

switch3_4_0

switch3_4_1

switch3_4_2

switch3_4_3

switch3_4_4

switch3_4_5

switch3_4_6

switch7_1_4

switch7_1_5

switch7_2_0

switch7_2_1

switch3_5_3

switch3_5_4

switch3_5_5

switch3_5_6

switch3_5_7

switch3_6_0

switch3_6_1

switch3_6_2

switch3_6_3

switch3_6_4

switch3_6_5

switch3_6_6

switch3_6_7

switch3_4_7

switch3_5_0

switch3_5_2

switch3_5_1

switch3_7_0

switch3_7_1

switch3_7_2

switch3_7_3

switch3_7_4

switch3_7_5

switch3_7_6

switch3_7_7

switch2_0_0

switch2_0_1

switch2_0_2

switch2_0_3

switch2_0_6

switch2_0_7

switch2_1_0

switch2_1_1

switch2_1_2

switch2_1_3

switch2_1_6

switch2_1_7

switch2_2_0

switch2_2_1

switch2_2_2

switch2_2_3

switch2_2_4

switch2_2_5

switch2_2_6

switch2_2_7

switch2_3_0

switch2_3_1

switch2_3_2

switch2_3_3

switch2_3_4

switch2_3_5

switch2_3_6

switch2_3_7

switch2_4_0

switch2_4_1

switch2_4_2

switch2_4_3

switch2_4_4

switch2_4_5

switch2_4_6

switch2_4_7

switch2_5_0

switch2_5_1

switch2_5_2

switch2_5_3

switch2_5_4

switch2_5_5

switch2_5_6

switch2_5_7

switch2_6_0

switch2_6_1

switch2_6_2

switch2_6_3

switch2_6_4

switch2_6_5

switch2_6_6

switch2_6_7

switch2_7_0

switch2_7_1

switch2_7_2

switch2_7_3

switch2_7_4

switch2_7_5

switch2_7_6

switch2_7_7

switch4_0_0

switch4_0_1

switch4_0_2

switch4_0_3

switch4_0_4

switch4_0_5

switch4_0_6

switch4_0_7

switch4_1_0

switch4_1_1

switch4_1_2

switch4_1_3

switch4_1_4

switch4_1_5

switch4_1_6

switch4_1_7

switch4_2_0

switch4_2_1

switch4_2_2

switch4_2_3

switch4_2_4

switch4_2_5

switch4_3_0

switch4_3_1

switch4_3_2

switch4_3_3

switch4_3_4

switch4_3_5

switch4_4_0

switch4_4_1

switch4_4_2

switch4_4_3

switch4_4_4

switch4_4_5

switch4_4_6

switch4_4_7

switch4_5_0

switch4_5_1

switch4_5_2

switch4_5_3

switch4_5_4

switch4_5_5

switch4_5_6

switch4_5_7

switch4_6_0

switch4_6_1

switch4_6_2

switch4_6_3

switch4_6_4

switch4_6_5

switch4_6_6

switch4_6_7

switch4_7_0

switch4_7_1

switch4_7_2

switch4_7_3

switch4_7_4

switch4_7_5

switch4_7_6

switch4_7_7

switch5_0_0

switch5_0_1

switch5_2_0

switch5_2_1

switch5_2_2

switch5_2_3

switch5_2_4

switch5_2_5

switch5_2_6

switch5_2_7

switch5_3_0

switch5_3_1

switch5_3_2

switch5_3_3

switch5_3_4

switch5_3_5

switch5_3_6

switch5_3_7

switch5_4_0

switch5_4_1

switch5_4_4

switch5_4_5

switch5_5_0

switch5_5_1

switch5_5_4

switch5_5_5

switch5_6_0

switch5_6_1

switch5_6_2

switch5_6_3

switch5_6_4

switch5_6_5

switch5_6_6

switch5_6_7

switch5_7_0

switch5_7_1

switch5_7_2

switch5_7_3

switch5_7_4

switch5_7_5

switch5_7_6

switch5_7_7

switch8_0_0

switch8_0_1

switch8_0_4

switch8_0_5

switch8_1_0

switch8_1_1

switch8_1_4

switch8_1_5

switch8_2_0

switch8_2_1

switch8_2_2

switch8_2_3

switch8_2_4

switch8_2_5

switch8_2_6

switch8_2_7

switch8_3_0

switch8_3_1

switch8_3_2

switch8_3_3

switch8_3_4

switch8_3_5

switch8_3_6

switch8_3_7

switch8_4_0

switch8_4_1

switch8_4_4

switch8_4_5

switch8_5_0

switch8_5_1

switch8_5_4

switch8_5_5

switch8_6_0

switch8_6_1

switch8_6_2

switch8_6_3

switch8_6_4

switch8_6_5

switch8_6_6

switch8_6_7

switch8_7_0

switch8_7_1

switch8_7_2

switch8_7_3

switch8_7_4

switch8_7_5

switch8_7_6

switch8_7_7

switch6_0_0

switch6_0_1

switch6_0_4

switch6_0_5

switch6_1_0

switch6_1_1

switch6_1_4

switch6_1_5

switch6_2_0

switch6_2_1

switch6_2_2

switch6_2_3

switch6_2_4

switch6_2_5

switch6_2_6

switch6_2_7

switch6_3_0

switch6_3_1

switch6_3_2

switch6_3_3

switch6_3_4

switch6_3_5

switch6_3_6

switch6_3_7

switch6_4_0

switch6_4_1

switch6_4_4

switch6_4_5

switch6_5_0

switch6_5_1

switch6_5_4

switch6_6_5

switch6_6_6

switch6_6_7

switch6_7_0

switch6_7_1

switch6_7_2

switch6_7_3

switch6_7_4

switch6_7_5

switch6_7_6

switch6_7_7

switch7_0_0

switch7_0_1

switch7_0_4

switch7_0_5

switch7_1_0

switch7_1_1

switch7_2_2

switch7_2_3

switch7_2_4

switch7_2_5

switch7_2_6

switch7_2_7

switch7_3_0

switch7_3_1

switch7_3_2

switch7_3_3

switch7_3_4

switch7_3_5

switch7_3_6

switch7_3_7

switch7_4_0

switch7_4_1

switch7_4_4

switch7_4_5

switch7_5_0

switch7_5_1

switch7_5_4

switch7_5_5

switch7_6_0

switch7_6_1

switch7_6_2

switch7_6_3

switch7_6_4

switch7_6_5

switch7_6_6

switch7_6_7

switch7_7_0

switch7_7_1

switch7_7_2

switch7_7_3

switch7_7_4

switch7_7_5

switch7_7_6

switch7_7_7

check for constant places

ok

check if there are places and transitions

ok

check if there are transitions without pre-places

ok

check if at least one transition is enabled in m0

ok

check if there are transitions that can never fire

ok

initing FirstDep: 0m 0.004sec

18222 23312 26903 41915

iterations count:424126 (414), effective:1828 (1)

initing FirstDep: 0m 0.004sec

18343 24575 27668

iterations count:348267 (340), effective:2253 (2)

15607 18953

iterations count:253374 (247), effective:1818 (1)

43220 49452 52545

iterations count:348267 (340), effective:2253 (2)

8750 11788

iterations count:244891 (239), effective:1777 (1)

23174 29097 33146 35492 37679 39838 41073 42007

iterations count:875740 (855), effective:4278 (4)

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="PermAdmissibility-COL-01"

export BK_EXAMINATION="ReachabilityCardinality"

export BK_TOOL="marcie"

export BK_RESULT_DIR="/tmp/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/PermAdmissibility-COL-01.tgz

mv PermAdmissibility-COL-01 execution

# this is for BenchKit: explicit launching of the test

cd execution

echo "====================================================================="

echo " Generated by BenchKit 2-3254"

echo " Executing tool marcie"

echo " Input is PermAdmissibility-COL-01, examination is ReachabilityCardinality"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 1"

echo " Run identifier is r031-blw7-149440474100349"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "ReachabilityCardinality" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "ReachabilityCardinality" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "ReachabilityCardinality.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property ReachabilityCardinality.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "ReachabilityCardinality.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;