About the Execution of ITS-Tools for S_SharedMemory-COL-000100

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 108.850 | 90.00 | 50.00 | 5.00 | 1.7013E+0051 1.7126E+0053 1 201 | normal |

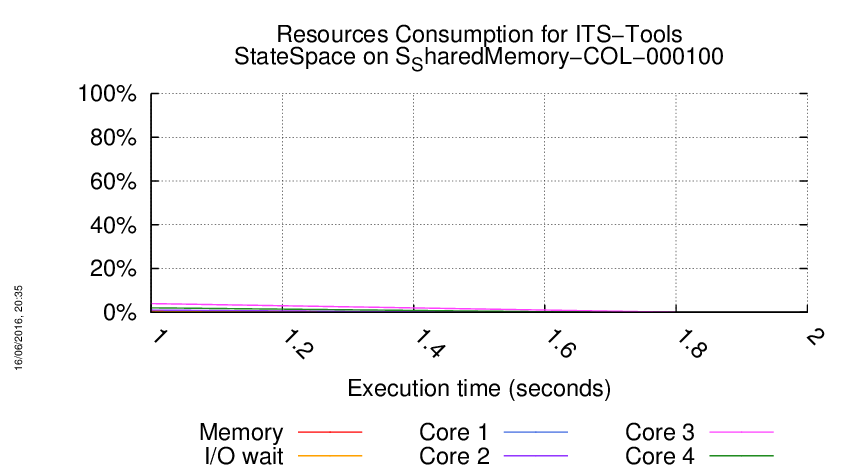

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

.............

=====================================================================

Generated by BenchKit 2-2979

Executing tool itstools

Input is S_SharedMemory-COL-000100, examination is StateSpace

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r181kn-smll-146444111600658

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

no data necessary for post analysis

=== Now, execution of the tool begins

BK_START 1464592664666

its-reach command run as :

/home/mcc/BenchKit//its-reach-linux64 -i modelMain.xml -t ITSXML -ssDR 5 --stats

Model in internal textual format :

TPNet Process {

// places definition

place Active ;

place OwnMemAcc ;

place Queue ;

place Ext_Mem_Acc_P ;

place Memory ;

place Ext_Mem_Acc_M ;

// states definition

state init{ Active = 1; Ext_Mem_Acc_M = 0; Ext_Mem_Acc_P = 0; Memory = 1; OwnMemAcc = 0; Queue = 0; }

// transitions definition

public transition elapse label "elapse" {

}

private transition T_8Begin_Own_Acc label "Begin_Own_Acc" {

in Active(1) ;

out OwnMemAcc(1) ;

}

private transition T_9End_Own_Acc label "End_Own_Acc" {

in OwnMemAcc(1) ;

out Active(1) ;

test Memory(1) ;

}

private transition T_10Req_Ext_Acc label "Req_Ext_Acc" {

in Active(1) ;

out Queue(1) ;

}

public transition T_11Begin_Ext_Acc_P label "Begin_Ext_Acc_P" {

in Queue(1) ;

out Ext_Mem_Acc_P(1) ;

}

public transition T_12End_Ext_Acc_P label "End_Ext_Acc_P" {

in Ext_Mem_Acc_P(1) ;

out Active(1) ;

}

public transition T_13End_Ext_Acc_M label "End_Ext_Acc_M" {

in Ext_Mem_Acc_M(1) ;

out Memory(1) ;

}

public transition T_14Begin_Ext_Acc_M label "Begin_Ext_Acc_M" {

in Memory(1) ;

out Ext_Mem_Acc_M(1) ;

inhibitor Ext_Mem_Acc_P(1) ;

}

}

ScalarSet Process[100] ProcSet {

// instance name

instanceName i_3_;

// states definition

state init{ instance[0] = init; }

// delegators

ANY delegator End_Ext_Acc_P label(End_Ext_Acc_P) ;

ANY delegator End_Ext_Acc_M label(End_Ext_Acc_M) ;

ANY delegator Begin_Ext_Acc_P label(Begin_Ext_Acc_P) ;

ANY delegator Begin_Ext_Acc_M label(Begin_Ext_Acc_M) ;

ALL delegator elapse label(elapse) ;

}

Encoded as a submodel :

TPNet Process {

// places definition

place Active ;

place OwnMemAcc ;

place Queue ;

place Ext_Mem_Acc_P ;

place Memory ;

place Ext_Mem_Acc_M ;

// states definition

state init{ Active = 1; Ext_Mem_Acc_M = 0; Ext_Mem_Acc_P = 0; Memory = 1; OwnMemAcc = 0; Queue = 0; }

// transitions definition

public transition elapse label "elapse" {

}

private transition T_8Begin_Own_Acc label "Begin_Own_Acc" {

in Active(1) ;

out OwnMemAcc(1) ;

}

private transition T_9End_Own_Acc label "End_Own_Acc" {

in OwnMemAcc(1) ;

out Active(1) ;

test Memory(1) ;

}

private transition T_10Req_Ext_Acc label "Req_Ext_Acc" {

in Active(1) ;

out Queue(1) ;

}

public transition T_11Begin_Ext_Acc_P label "Begin_Ext_Acc_P" {

in Queue(1) ;

out Ext_Mem_Acc_P(1) ;

}

public transition T_12End_Ext_Acc_P label "End_Ext_Acc_P" {

in Ext_Mem_Acc_P(1) ;

out Active(1) ;

}

public transition T_13End_Ext_Acc_M label "End_Ext_Acc_M" {

in Ext_Mem_Acc_M(1) ;

out Memory(1) ;

}

public transition T_14Begin_Ext_Acc_M label "Begin_Ext_Acc_M" {

in Memory(1) ;

out Ext_Mem_Acc_M(1) ;

inhibitor Ext_Mem_Acc_P(1) ;

}

}

Composite Process_4 {

// subnets

Process i_3__0 ;

Process i_3__1 ;

Process i_3__2 ;

Process i_3__3 ;

// nested exposed variables

// states definition

state init{ i_3__0 = init; i_3__1 = init; i_3__2 = init; i_3__3 = init; }

// synchronizations

synchronization End_Ext_Acc_P0 label "End_Ext_Acc_P" {

i_3__0."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P1 label "End_Ext_Acc_P" {

i_3__1."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P2 label "End_Ext_Acc_P" {

i_3__2."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P3 label "End_Ext_Acc_P" {

i_3__3."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_M0 label "End_Ext_Acc_M" {

i_3__0."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M1 label "End_Ext_Acc_M" {

i_3__1."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M2 label "End_Ext_Acc_M" {

i_3__2."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M3 label "End_Ext_Acc_M" {

i_3__3."End_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_P0 label "Begin_Ext_Acc_P" {

i_3__0."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P1 label "Begin_Ext_Acc_P" {

i_3__1."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P2 label "Begin_Ext_Acc_P" {

i_3__2."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P3 label "Begin_Ext_Acc_P" {

i_3__3."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_M0 label "Begin_Ext_Acc_M" {

i_3__0."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M1 label "Begin_Ext_Acc_M" {

i_3__1."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M2 label "Begin_Ext_Acc_M" {

i_3__2."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M3 label "Begin_Ext_Acc_M" {

i_3__3."Begin_Ext_Acc_M" ;

}

synchronization elapse label "elapse" {

i_3__0."elapse" ;

i_3__1."elapse" ;

i_3__2."elapse" ;

i_3__3."elapse" ;

}

}

Composite Process_20 {

// subnets

Process_4 i_3__0 ;

Process_4 i_3__1 ;

Process_4 i_3__2 ;

Process_4 i_3__3 ;

Process_4 i_3__4 ;

// nested exposed variables

// states definition

state init{ i_3__0 = init; i_3__1 = init; i_3__2 = init; i_3__3 = init; i_3__4 = init; }

// synchronizations

synchronization End_Ext_Acc_P0 label "End_Ext_Acc_P" {

i_3__0."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P1 label "End_Ext_Acc_P" {

i_3__1."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P2 label "End_Ext_Acc_P" {

i_3__2."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P3 label "End_Ext_Acc_P" {

i_3__3."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P4 label "End_Ext_Acc_P" {

i_3__4."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_M0 label "End_Ext_Acc_M" {

i_3__0."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M1 label "End_Ext_Acc_M" {

i_3__1."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M2 label "End_Ext_Acc_M" {

i_3__2."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M3 label "End_Ext_Acc_M" {

i_3__3."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M4 label "End_Ext_Acc_M" {

i_3__4."End_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_P0 label "Begin_Ext_Acc_P" {

i_3__0."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P1 label "Begin_Ext_Acc_P" {

i_3__1."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P2 label "Begin_Ext_Acc_P" {

i_3__2."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P3 label "Begin_Ext_Acc_P" {

i_3__3."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P4 label "Begin_Ext_Acc_P" {

i_3__4."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_M0 label "Begin_Ext_Acc_M" {

i_3__0."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M1 label "Begin_Ext_Acc_M" {

i_3__1."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M2 label "Begin_Ext_Acc_M" {

i_3__2."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M3 label "Begin_Ext_Acc_M" {

i_3__3."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M4 label "Begin_Ext_Acc_M" {

i_3__4."Begin_Ext_Acc_M" ;

}

synchronization elapse label "elapse" {

i_3__0."elapse" ;

i_3__1."elapse" ;

i_3__2."elapse" ;

i_3__3."elapse" ;

i_3__4."elapse" ;

}

}

Composite Process_100 {

// subnets

Process_20 i_3__0 ;

Process_20 i_3__1 ;

Process_20 i_3__2 ;

Process_20 i_3__3 ;

Process_20 i_3__4 ;

// nested exposed variables

// states definition

state init{ i_3__0 = init; i_3__1 = init; i_3__2 = init; i_3__3 = init; i_3__4 = init; }

// synchronizations

synchronization End_Ext_Acc_P0 label "End_Ext_Acc_P" {

i_3__0."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P1 label "End_Ext_Acc_P" {

i_3__1."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P2 label "End_Ext_Acc_P" {

i_3__2."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P3 label "End_Ext_Acc_P" {

i_3__3."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_P4 label "End_Ext_Acc_P" {

i_3__4."End_Ext_Acc_P" ;

}

synchronization End_Ext_Acc_M0 label "End_Ext_Acc_M" {

i_3__0."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M1 label "End_Ext_Acc_M" {

i_3__1."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M2 label "End_Ext_Acc_M" {

i_3__2."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M3 label "End_Ext_Acc_M" {

i_3__3."End_Ext_Acc_M" ;

}

synchronization End_Ext_Acc_M4 label "End_Ext_Acc_M" {

i_3__4."End_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_P0 label "Begin_Ext_Acc_P" {

i_3__0."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P1 label "Begin_Ext_Acc_P" {

i_3__1."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P2 label "Begin_Ext_Acc_P" {

i_3__2."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P3 label "Begin_Ext_Acc_P" {

i_3__3."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_P4 label "Begin_Ext_Acc_P" {

i_3__4."Begin_Ext_Acc_P" ;

}

synchronization Begin_Ext_Acc_M0 label "Begin_Ext_Acc_M" {

i_3__0."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M1 label "Begin_Ext_Acc_M" {

i_3__1."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M2 label "Begin_Ext_Acc_M" {

i_3__2."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M3 label "Begin_Ext_Acc_M" {

i_3__3."Begin_Ext_Acc_M" ;

}

synchronization Begin_Ext_Acc_M4 label "Begin_Ext_Acc_M" {

i_3__4."Begin_Ext_Acc_M" ;

}

synchronization elapse label "elapse" {

i_3__0."elapse" ;

i_3__1."elapse" ;

i_3__2."elapse" ;

i_3__3."elapse" ;

i_3__4."elapse" ;

}

}

TPNet Bus {

// places definition

place Ext_Bus ;

// states definition

state init{ Ext_Bus = 1; }

// transitions definition

public transition elapse label "elapse" {

}

public transition T_4lock label "lock" {

in Ext_Bus(1) ;

}

public transition T_5release label "release" {

out Ext_Bus(1) ;

}

}

Composite SharedMem {

// subnets

ProcSet pset ;

Bus bus ;

// nested exposed variables

// states definition

state init{ bus = init; pset = init; }

// synchronizations

synchronization elapse label "elapse" {

pset."elapse" ;

bus."elapse" ;

}

synchronization Begin_Ext_Acc label "" {

pset."Begin_Ext_Acc_P" ;

pset."Begin_Ext_Acc_M" ;

bus."lock" ;

}

synchronization sync0 label "" {

bus."release" ;

pset."End_Ext_Acc_P" ;

pset."End_Ext_Acc_M" ;

}

}

// target model :

main:SharedMem = init ;

[ pset={[ i_3__4={[ i_3__4={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__3={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__2={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__1={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__0={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} ]

} i_3__3={[ i_3__4={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__3={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__2={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__1={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__0={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} ]

} i_3__2={[ i_3__4={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__3={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__2={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__1={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__0={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} ]

} i_3__1={[ i_3__4={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__3={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__2={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__1={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__0={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} ]

} i_3__0={[ i_3__4={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__3={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__2={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__1={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} i_3__0={[ i_3__3={[ Memory={1} Active={1} ]} i_3__2={[ Memory={1} Active={1} ]} i_3__1={[ Memory={1} Active={1} ]} i_3__0={[ Memory={1} Active={1} ]} ]

} ]

} ]

} bus={[ Ext_Bus={1} ]} ]

Some reachable states : [ 1.70126e+51 states ]Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

SharedMem,1.70126e+51,0.02439,5648,71,3,1033,12,140,1347,7,10,0

Total reachable state count : 1.701261195936369403720401762795966984683e+51

STATE_SPACE MAX_TOKEN_IN_PLACE 1

STATE_SPACE MAX_TOKEN_PER_MARKING 201

STATE_SPACE STATES 1701261195936369403751358189356315821189656930125301

STATE_SPACE TRANSITIONS 171259950139247365303416033421115948918910329560932300

BK_STOP 1464592664756

--------------------

content from stderr:

+ export BINDIR=/home/mcc/BenchKit/

+ BINDIR=/home/mcc/BenchKit/

++ pwd

+ export MODEL=/home/mcc/execution

+ MODEL=/home/mcc/execution

+ [[ StateSpace = StateSpace ]]

+ [[ -f modelMain.xml ]]

+ /home/mcc/BenchKit//its-reach-linux64 -i modelMain.xml -t ITSXML -ssDR 5 --stats

+ sed 's/Max variable value :/STATE_SPACE MAX_TOKEN_IN_PLACE /'

+ sed 's/Exact state count :/STATE_SPACE STATES /'

+ sed 's/Maximum sum along a path :/STATE_SPACE MAX_TOKEN_PER_MARKING /'

+ sed 's/Total edges in reachability graph :/STATE_SPACE TRANSITIONS /'

built 2 ordering constraints for composite.

(order - FORCE) initial cost 4 / final cost 4

built 21 ordering constraints for composite.

(order - FORCE) initial cost 48 / final cost 48

built 21 ordering constraints for composite.

(order - FORCE) initial cost 48 / final cost 48

built 17 ordering constraints for composite.

(order - FORCE) initial cost 30 / final cost 30

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="S_SharedMemory-COL-000100"

export BK_EXAMINATION="StateSpace"

export BK_TOOL="itstools"

export BK_RESULT_DIR="/root/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/S_SharedMemory-COL-000100.tgz

mv S_SharedMemory-COL-000100 execution

# this is for BenchKit: explicit launching of the test

cd execution

echo "====================================================================="

echo " Generated by BenchKit 2-2979"

echo " Executing tool itstools"

echo " Input is S_SharedMemory-COL-000100, examination is StateSpace"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r181kn-smll-146444111600658"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "StateSpace" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "StateSpace" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "StateSpace.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property StateSpace.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "StateSpace.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;