About the Execution of ITS-Tools for SharedMemory-PT-000005

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 314.080 | 4698.00 | 9874.00 | 288.60 | FFFFTTTFTTFFTTTT | normal |

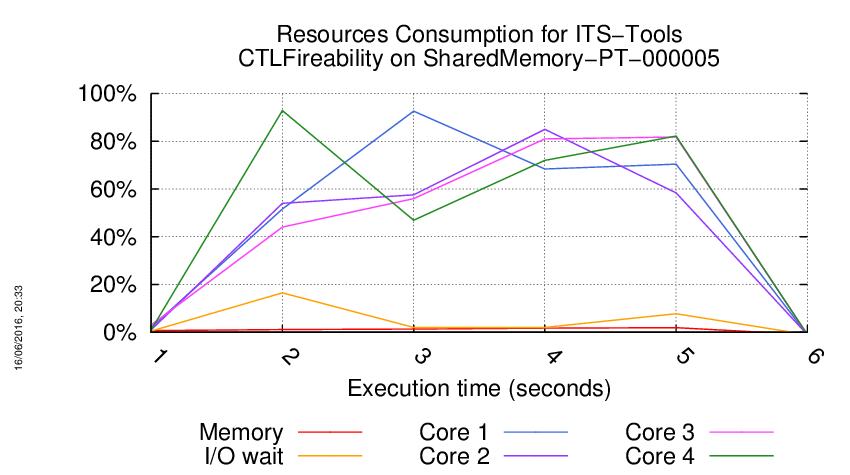

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

....................................

=====================================================================

Generated by BenchKit 2-2979

Executing tool itstools

Input is SharedMemory-PT-000005, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r109kn-smll-146373287500355

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-0

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-1

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-10

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-11

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-12

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-13

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-14

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-15

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-2

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-3

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-4

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-5

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-6

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-7

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-8

FORMULA_NAME SharedMemory-COL-000005-CTLFireability-9

=== Now, execution of the tool begins

BK_START 1464037141620

its-ctl command run as :

/home/mcc/BenchKit/eclipse/plugins/fr.lip6.move.gal.itstools.binaries_1.0.0.201605191313/bin/its-ctl-linux64 --gc-threshold 2000000 --quiet -i /home/mcc/execution/CTLFireability.gal -t CGAL -ctl /home/mcc/execution/CTLFireability.ctl

No direction supplied, using forward translation only.

Parsed 16 CTL formulae.

Model ,|S| ,Time ,Mem(kb) ,fin. SDD ,fin. DDD ,peak SDD ,peak DDD ,SDD Hom ,SDD cache peak ,DDD Hom ,DDD cachepeak ,SHom cache

reachable,1863,0.036566,5088,2,593,5,1830,6,0,222,1126,0

Converting to forward existential form...Done !

original formula: EF(AG(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))

=> equivalent forward existential formula: [(FwdU(Init,TRUE) * !(E(TRUE U !(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))))] != FALSE

Checking (exact) 0 :[(FwdU(Init,TRUE) * !(E(TRUE U !(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))))] != FALSE

Checking (exact) 0 :(FwdU(Init,TRUE) * !(E(TRUE U !(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))))

Checking (exact) 1 :!(E(TRUE U !(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))))

Checking (exact) 1 :E(TRUE U !(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))

Checking (exact) 1 :!(EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))

Checking (exact) 1 :EX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))

(forward)formula 0,0,0.164661,7880,1,0,8,20112,37,1,1103,7983,6

FORMULA SharedMemory-COL-000005-CTLFireability-0 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: E(AF((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1))) U AG(!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))

=> equivalent forward existential formula: [(FwdU(Init,!(EG(!((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * !(E(TRUE U !(!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))))] != FALSE

Checking (exact) 0 :[(FwdU(Init,!(EG(!((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * !(E(TRUE U !(!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))))] != FALSE

Checking (exact) 0 :(FwdU(Init,!(EG(!((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * !(E(TRUE U !(!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))))

Checking (exact) 1 :!(E(TRUE U !(!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))))

Checking (exact) 1 :E(TRUE U !(!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))

(forward)formula 1,0,0.173219,8148,1,0,9,20173,76,1,1140,7997,9

FORMULA SharedMemory-COL-000005-CTLFireability-1 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: AG(((EF(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))) + ((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))) * AF((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))))

=> equivalent forward existential formula: ([((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))) * !((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))] = FALSE * [FwdG((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))),!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))] = FALSE)

Checking (exact) 0 :([((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))) * !((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))] = FALSE * [FwdG((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))),!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))] = FALSE)

Checking (exact) 1 :[FwdG((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))),!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))] = FALSE

Checking (exact) 0 :FwdG((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))),!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))

Checking (exact) 1 :(FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))

Checking (exact) 1 :!((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

Checking (exact) 1 :(E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))

Checking (exact) 1 :E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))

Checking (exact) 1 :[((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))) * !((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))] = FALSE

Checking (exact) 0 :((FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))) * !((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))

Checking (exact) 1 :!((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))))

Checking (exact) 1 :(FwdU(Init,TRUE) * !((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))

Checking (exact) 1 :!((E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

Checking (exact) 1 :(E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)) + !((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))

Checking (exact) 1 :E(TRUE U ((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))

(forward)formula 2,1,0.237169,9628,1,0,14,24438,199,3,1417,12621,17

FORMULA SharedMemory-COL-000005-CTLFireability-2 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: AG((EX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))) + !(((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))))))

=> equivalent forward existential formula: [((FwdU(Init,TRUE) * !(!(((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))) * !(EX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))))] = FALSE

Checking (exact) 0 :[((FwdU(Init,TRUE) * !(!(((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))) * !(EX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))))] = FALSE

Checking (exact) 0 :((FwdU(Init,TRUE) * !(!(((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) * ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))) * !(EX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))))

Checking (exact) 1 :!(EX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))

Checking (exact) 1 :EX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))

(forward)formula 3,1,0.252516,9832,1,0,15,25268,200,3,1441,12981,19

FORMULA SharedMemory-COL-000005-CTLFireability-3 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: E(AX((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))) U AG((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

=> equivalent forward existential formula: [(FwdU(Init,!(EX(!((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))) * !(E(TRUE U !((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))))] != FALSE

Checking (exact) 0 :[(FwdU(Init,!(EX(!((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))) * !(E(TRUE U !((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))))] != FALSE

Checking (exact) 0 :(FwdU(Init,!(EX(!((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))) * !(E(TRUE U !((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))))

Checking (exact) 1 :!(E(TRUE U !((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))

Checking (exact) 1 :E(TRUE U !((((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

(forward)formula 4,0,0.31125,10192,1,0,16,25925,202,3,1452,13651,22

FORMULA SharedMemory-COL-000005-CTLFireability-4 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: E(A((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1) U ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) U ((((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))) * AX((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))

=> equivalent forward existential formula: [((FwdU(Init,!((E(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) U (!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))) + EG(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * (((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))) * !(EX(!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))))] != FALSE

Checking (exact) 0 :[((FwdU(Init,!((E(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) U (!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))) + EG(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * (((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))) * !(EX(!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))))] != FALSE

Checking (exact) 0 :((FwdU(Init,!((E(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) U (!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))) + EG(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * (((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))) * !(EX(!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))))

Checking (exact) 1 :!(EX(!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)))))

Checking (exact) 1 :EX(!((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1))))

Checking (exact) 1 :(FwdU(Init,!((E(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) U (!((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)) * !(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))) + EG(!(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)))))) * (((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))))

Checking (exact) 1 :(((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1) * !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))

Checking (exact) 1 :!(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))

(forward)formula 5,0,0.346818,10452,1,0,19,31435,205,6,1454,18033,23

FORMULA SharedMemory-COL-000005-CTLFireability-5 FALSE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is FALSE !

***************************************

original formula: EF(AX((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))

=> equivalent forward existential formula: [(FwdU(Init,TRUE) * !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))] != FALSE

Checking (exact) 0 :[(FwdU(Init,TRUE) * !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))] != FALSE

Checking (exact) 0 :(FwdU(Init,TRUE) * !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))

Checking (exact) 1 :!(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

Checking (exact) 1 :EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))

Checking (exact) 1 :FwdU(Init,TRUE)

Checking (exact) 1 :Init

(forward)formula 6,1,0.372674,10620,1,0,21,32210,205,8,1454,19265,24

FORMULA SharedMemory-COL-000005-CTLFireability-6 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: AF(EF(AX((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

=> equivalent forward existential formula: [FwdG(Init,!(E(TRUE U !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))))] = FALSE

Checking (exact) 0 :[FwdG(Init,!(E(TRUE U !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))))] = FALSE

Checking (exact) 0 :FwdG(Init,!(E(TRUE U !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))))

Checking (exact) 1 :Init

Checking (exact) 1 :!(E(TRUE U !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))))

Checking (exact) 1 :E(TRUE U !(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))))

Checking (exact) 1 :!(EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))

Checking (exact) 1 :EX(!((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))))

(forward)formula 7,1,0.406462,10812,1,0,21,32362,208,8,1454,19381,26

FORMULA SharedMemory-COL-000005-CTLFireability-7 TRUE TECHNIQUES DECISION_DIAGRAMS TOPOLOGICAL

Formula is TRUE !

***************************************

original formula: (((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))) + AG((((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1))))) * EF((((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))

=> equivalent forward existential formula: ([(FwdU((Init * !((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))),TRUE) * !((((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))] = FALSE * [(Init * !(E(TRUE U (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))] = FALSE)

Checking (exact) 0 :([(FwdU((Init * !((((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) + (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1))) + ((((((OwnMemAcc_5>=1 * Memory_5>=1) + (OwnMemAcc_4>=1 * Memory_4>=1)) + (OwnMemAcc_1>=1 * Memory_1>=1)) + (OwnMemAcc_3>=1 * Memory_3>=1)) + (OwnMemAcc_2>=1 * Memory_2>=1)) * (((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)))))),TRUE) * !((((((((((((((((((((((((Ext_Bus>=1 * Memory_2>=1) * Queue_1>=1) + ((Ext_Bus>=1 * Queue_3>=1) * Memory_2>=1)) + ((Ext_Bus>=1 * Queue_4>=1) * Memory_2>=1)) + ((Queue_5>=1 * Memory_2>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_1>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_3>=1)) + ((Ext_Bus>=1 * Memory_1>=1) * Queue_4>=1)) + ((Memory_1>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_4>=1) * Queue_1>=1)) + ((Ext_Bus>=1 * Queue_2>=1) * Memory_4>=1)) + ((Queue_3>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Queue_5>=1 * Memory_4>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Queue_1>=1) * Memory_3>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_2>=1)) + ((Ext_Bus>=1 * Memory_3>=1) * Queue_4>=1)) + ((Memory_3>=1 * Queue_5>=1) * Ext_Bus>=1)) + ((Ext_Bus>=1 * Memory_5>=1) * Queue_2>=1)) + ((Queue_1>=1 * Memory_5>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_4>=1) * Ext_Bus>=1)) + ((Memory_5>=1 * Queue_3>=1) * Ext_Bus>=1)) + ((((Active_2>=1 + Active_1>=1) + Active_5>=1) + Active_3>=1) + Active_4>=1)) + !(((((Active_2>=1 + Active_1>=1) + Active_4>=1) + Active_3>=1) + Active_5>=1)))))] = FALSE * [(Init * !(E(TRUE U (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))] = FALSE)

Checking (exact) 1 :[(Init * !(E(TRUE U (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))] = FALSE

Checking (exact) 0 :(Init * !(E(TRUE U (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))))

Checking (exact) 1 :!(E(TRUE U (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1)))

Checking (exact) 1 :E(TRUE U (((((((((((((((((((Ext_Mem_Acc_4_1>=1 + Ext_Mem_Acc_5_1>=1) + Ext_Mem_Acc_2_1>=1) + Ext_Mem_Acc_3_1>=1) + Ext_Mem_Acc_5_2>=1) + Ext_Mem_Acc_4_2>=1) + Ext_Mem_Acc_3_2>=1) + Ext_Mem_Acc_1_2>=1) + Ext_Mem_Acc_5_3>=1) + Ext_Mem_Acc_4_3>=1) + Ext_Mem_Acc_2_3>=1) + Ext_Mem_Acc_1_3>=1) + Ext_Mem_Acc_5_4>=1) + Ext_Mem_Acc_3_4>=1) + Ext_Mem_Acc_2_4>=1) + Ext_Mem_Acc_1_4>=1) + Ext_Mem_Acc_4_5>=1) + Ext_Mem_Acc_3_5>=1) + Ext_Mem_Acc_2_5>=1) + Ext_Mem_Acc_1_5>=1))