About the Execution of Tapaal(PAR) for NeoElection-PT-4

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 113.400 | 637.00 | 50.00 | 2.50 | [undef] | Cannot compute |

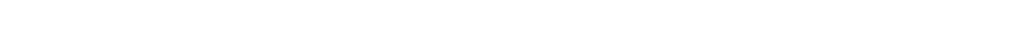

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

...........

=====================================================================

Generated by BenchKit 2-2979

Executing tool tapaalPAR

Input is NeoElection-PT-4, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 4

Run identifier is r076kn-smll-146363814200094

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME NeoElection-COL-4-CTLFireability-0

FORMULA_NAME NeoElection-COL-4-CTLFireability-1

FORMULA_NAME NeoElection-COL-4-CTLFireability-10

FORMULA_NAME NeoElection-COL-4-CTLFireability-11

FORMULA_NAME NeoElection-COL-4-CTLFireability-12

FORMULA_NAME NeoElection-COL-4-CTLFireability-13

FORMULA_NAME NeoElection-COL-4-CTLFireability-14

FORMULA_NAME NeoElection-COL-4-CTLFireability-15

FORMULA_NAME NeoElection-COL-4-CTLFireability-2

FORMULA_NAME NeoElection-COL-4-CTLFireability-3

FORMULA_NAME NeoElection-COL-4-CTLFireability-4

FORMULA_NAME NeoElection-COL-4-CTLFireability-5

FORMULA_NAME NeoElection-COL-4-CTLFireability-6

FORMULA_NAME NeoElection-COL-4-CTLFireability-7

FORMULA_NAME NeoElection-COL-4-CTLFireability-8

FORMULA_NAME NeoElection-COL-4-CTLFireability-9

=== Now, execution of the tool begins

BK_START 1463652783628

**********************************************

* TAPAAL Parallel verifying CTLFireability *

**********************************************

BK_STOP 1463652784265

--------------------

content from stderr:

/home/mcc/BenchKit/bin/ctl.sh: line 82: 359 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 361 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 363 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 365 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 367 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 369 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 371 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 373 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 375 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 377 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 379 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 381 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 383 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 385 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 387 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 82: 389 Illegal instruction timeout $TIMEOUT_SEQ $VERIFYPN_SEQ -ctl czero -s DFS -n -x $i model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 391 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 393 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 395 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 397 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 399 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 401 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 403 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 405 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 407 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 409 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 411 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 413 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 415 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 417 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 419 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 90: 421 Illegal instruction timeout $TIMEOUT_COM $VERIFYPN_COM -ctl czero -s DFS -n -x $j model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 423 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 425 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 427 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 429 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 431 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 433 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 435 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 437 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 439 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 441 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 443 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 445 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 447 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 449 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 451 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 98: 455 Illegal instruction timeout $TIMEOUT_PAR $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 457 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 458 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 459 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 460 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 461 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 462 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 463 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 464 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 465 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 466 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 467 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 468 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 469 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 470 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 471 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

/home/mcc/BenchKit/bin/ctl.sh: line 105: 472 Illegal instruction $VERIFYPN_PAR -ctl par -s DFS -n -x $k model.pnml CTLFireability.xml

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="NeoElection-PT-4"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="tapaalPAR"

export BK_RESULT_DIR="/root/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/NeoElection-PT-4.tgz

mv NeoElection-PT-4 execution

# this is for BenchKit: explicit launching of the test

cd execution

echo "====================================================================="

echo " Generated by BenchKit 2-2979"

echo " Executing tool tapaalPAR"

echo " Input is NeoElection-PT-4, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 4"

echo " Run identifier is r076kn-smll-146363814200094"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "UpperBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;