About the Execution of Marcie for PermAdmissibility-COL-01

| Execution Summary | |||||

| Max Memory Used (MB) |

Time wait (ms) | CPU Usage (ms) | I/O Wait (ms) | Computed Result | Execution Status |

| 3997.070 | 87045.00 | 87048.00 | 20.00 | ???????????????? | normal |

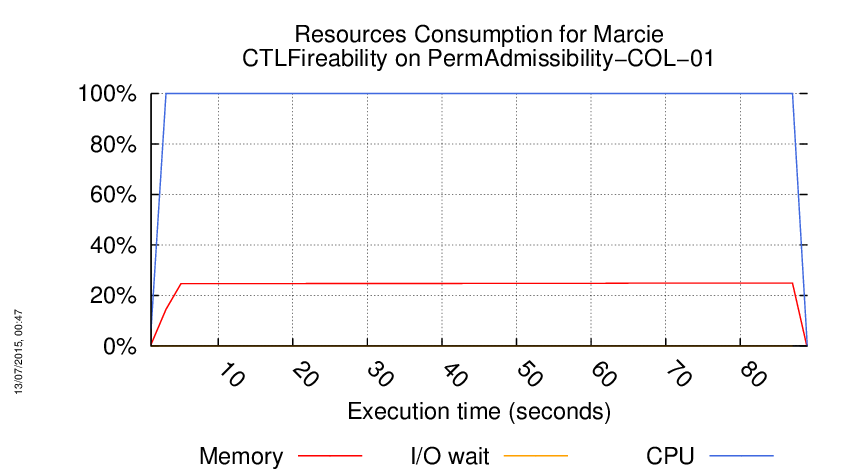

Execution Chart

We display below the execution chart for this examination (boot time has been removed).

Trace from the execution

Waiting for the VM to be ready (probing ssh)

.........

=====================================================================

Generated by BenchKit 2-2265

Executing tool marcie

Input is PermAdmissibility-COL-01, examination is CTLFireability

Time confinement is 3600 seconds

Memory confinement is 16384 MBytes

Number of cores is 1

Run identifier is r064kn-blw3-143254880300081

=====================================================================

--------------------

content from stdout:

=== Data for post analysis generated by BenchKit (invocation template)

The expected result is a vector of booleans

BOOL_VECTOR

here is the order used to build the result vector(from text file)

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-0

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-1

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-10

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-11

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-12

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-13

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-14

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-15

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-2

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-3

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-4

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-5

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-6

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-7

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-8

FORMULA_NAME PermAdmissibility-COL-01-CTLFireability-9

=== Now, execution of the tool begins

BK_START 1432725013521

Model: PermAdmissibility-COL-01

reachability algorithm:

Saturation-based algorithm

variable ordering algorithm:

Calculated like in [Noa99]

--memory=6 --suppress --rs-algorithm=3 --place-order=5

Marcie rev. 1429:1432M (built: crohr on 2014-10-22)

A model checker for Generalized Stochastic Petri nets

authors: Alex Tovchigrechko (IDD package and CTL model checking)

Martin Schwarick (Symbolic numerical analysis and CSL model checking)

Christian Rohr (Simulative and approximative numerical model checking)

marcie@informatik.tu-cottbus.de

called as: marcie --net-file=model.pnml --mcc-file=CTLFireability.xml --memory=6 --suppress --rs-algorithm=3 --place-order=5

parse successfull

net created successfully

Unfolding complete |P|=208|T|=1024|A|=6080

Time for unfolding: 0m0sec

(NrP: 208 NrTr: 1024 NrArc: 5984)

net check time: 0m0sec

parse formulas successfull

formulas created successfully

place and transition orderings generation:0m0sec

init dd package: 0m2sec

RS generation: 0m37sec

-> reachability set: #nodes 54981 (5.5e+04) #states 52,537 (4)

starting MCC model checker

--------------------------

checking: E [~ [IS-FIREABLE [switch9]] U AG [~ [IS-FIREABLE [switch7]]]]

normalized: E [~ [IS-FIREABLE [switch9]] U ~ [E [true U IS-FIREABLE [switch7]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-0CANNOT_COMPUTE

MC time: 0m0sec

checking: AF [[EX [IS-FIREABLE [display2]] & [[IS-FIREABLE [switch11] | IS-FIREABLE [switch9]] & [[IS-FIREABLE [switch10] | IS-FIREABLE [switch10]] & [IS-FIREABLE [switch8] & IS-FIREABLE [switch2]]]]]]

normalized: ~ [EG [~ [[EX [IS-FIREABLE [display2]] & [[IS-FIREABLE [switch11] | IS-FIREABLE [switch9]] & [[IS-FIREABLE [switch10] | IS-FIREABLE [switch10]] & [IS-FIREABLE [switch8] & IS-FIREABLE [switch2]]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-1CANNOT_COMPUTE

MC time: 0m0sec

checking: [~ [~ [[~ [IS-FIREABLE [switch10]] & AF [IS-FIREABLE [switch12]]]]] & AF [[IS-FIREABLE [switch1] & EF [IS-FIREABLE [switch6]]]]]

normalized: [[~ [IS-FIREABLE [switch10]] & ~ [EG [~ [IS-FIREABLE [switch12]]]]] & ~ [EG [~ [[IS-FIREABLE [switch1] & E [true U IS-FIREABLE [switch6]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-2CANNOT_COMPUTE

MC time: 0m0sec

checking: AG [~ [EF [[IS-FIREABLE [display4] & IS-FIREABLE [switch9]]]]]

normalized: ~ [E [true U E [true U [IS-FIREABLE [display4] & IS-FIREABLE [switch9]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-3CANNOT_COMPUTE

MC time: 0m0sec

checking: EX [AG [[[IS-FIREABLE [switch10] & IS-FIREABLE [display3]] | ~ [IS-FIREABLE [display3]]]]]

normalized: EX [~ [E [true U ~ [[[IS-FIREABLE [switch10] & IS-FIREABLE [display3]] | ~ [IS-FIREABLE [display3]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-4CANNOT_COMPUTE

MC time: 0m0sec

checking: [AG [AF [IS-FIREABLE [switch2]]] & ~ [EG [AF [IS-FIREABLE [switch10]]]]]

normalized: [~ [E [true U EG [~ [IS-FIREABLE [switch2]]]]] & ~ [EG [~ [EG [~ [IS-FIREABLE [switch10]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-5CANNOT_COMPUTE

MC time: 0m0sec

checking: EG [[~ [IS-FIREABLE [display2]] | A [IS-FIREABLE [switch9] U IS-FIREABLE [switch12]]]]

normalized: EG [[~ [IS-FIREABLE [display2]] | [~ [E [~ [IS-FIREABLE [switch9]] U [~ [IS-FIREABLE [switch12]] & ~ [IS-FIREABLE [switch9]]]]] & ~ [EG [~ [IS-FIREABLE [switch12]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-6CANNOT_COMPUTE

MC time: 0m0sec

checking: ~ [EF [[EF [IS-FIREABLE [switch12]] | AX [IS-FIREABLE [display4]]]]]

normalized: ~ [E [true U [E [true U IS-FIREABLE [switch12]] | ~ [EX [~ [IS-FIREABLE [display4]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-7CANNOT_COMPUTE

MC time: 0m0sec

checking: ~ [[AX [IS-FIREABLE [display3]] | [AF [IS-FIREABLE [display1]] | [IS-FIREABLE [switch8] | IS-FIREABLE [display3]]]]]

normalized: ~ [[~ [EX [~ [IS-FIREABLE [display3]]]] | [~ [EG [~ [IS-FIREABLE [display1]]]] | [IS-FIREABLE [switch8] | IS-FIREABLE [display3]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-8CANNOT_COMPUTE

MC time: 0m0sec

checking: [E [EX [IS-FIREABLE [switch12]] U EG [IS-FIREABLE [switch5]]] | [E [[IS-FIREABLE [display2] | IS-FIREABLE [switch1]] U [IS-FIREABLE [switch5] | IS-FIREABLE [display3]]] | EF [[IS-FIREABLE [switch1] & IS-FIREABLE [switch3]]]]]

normalized: [E [EX [IS-FIREABLE [switch12]] U EG [IS-FIREABLE [switch5]]] | [E [[IS-FIREABLE [display2] | IS-FIREABLE [switch1]] U [IS-FIREABLE [switch5] | IS-FIREABLE [display3]]] | E [true U [IS-FIREABLE [switch1] & IS-FIREABLE [switch3]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-9CANNOT_COMPUTE

MC time: 0m0sec

checking: EF [EG [AG [IS-FIREABLE [switch10]]]]

normalized: E [true U EG [~ [E [true U ~ [IS-FIREABLE [switch10]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-10CANNOT_COMPUTE

MC time: 0m0sec

checking: EF [[A [IS-FIREABLE [switch10] U IS-FIREABLE [display3]] | EG [~ [IS-FIREABLE [switch5]]]]]

normalized: E [true U [[~ [E [~ [IS-FIREABLE [switch10]] U [~ [IS-FIREABLE [display3]] & ~ [IS-FIREABLE [switch10]]]]] & ~ [EG [~ [IS-FIREABLE [display3]]]]] | EG [~ [IS-FIREABLE [switch5]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-11CANNOT_COMPUTE

MC time: 0m0sec

checking: AF [~ [[[[IS-FIREABLE [display2] | IS-FIREABLE [switch2]] & ~ [IS-FIREABLE [display2]]] | EF [IS-FIREABLE [display4]]]]]

normalized: ~ [EG [[[[IS-FIREABLE [display2] | IS-FIREABLE [switch2]] & ~ [IS-FIREABLE [display2]]] | E [true U IS-FIREABLE [display4]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-12CANNOT_COMPUTE

MC time: 0m0sec

checking: E [~ [AF [IS-FIREABLE [display1]]] U [[[IS-FIREABLE [switch7] & IS-FIREABLE [switch8]] | IS-FIREABLE [display3]] & AX [IS-FIREABLE [switch11]]]]

normalized: E [EG [~ [IS-FIREABLE [display1]]] U [[IS-FIREABLE [display3] | [IS-FIREABLE [switch7] & IS-FIREABLE [switch8]]] & ~ [EX [~ [IS-FIREABLE [switch11]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-13CANNOT_COMPUTE

MC time: 0m0sec

checking: AF [IS-FIREABLE [display4]]

normalized: ~ [EG [~ [IS-FIREABLE [display4]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-14CANNOT_COMPUTE

MC time: 0m0sec

checking: [~ [EG [~ [[IS-FIREABLE [switch6] & IS-FIREABLE [switch10]]]]] | [~ [A [IS-FIREABLE [display3] U IS-FIREABLE [switch5]]] & IS-FIREABLE [switch8]]]

normalized: [~ [EG [~ [[IS-FIREABLE [switch6] & IS-FIREABLE [switch10]]]]] | [IS-FIREABLE [switch8] & ~ [[~ [E [~ [IS-FIREABLE [display3]] U [~ [IS-FIREABLE [switch5]] & ~ [IS-FIREABLE [display3]]]]] & ~ [EG [~ [IS-FIREABLE [switch5]]]]]]]]

FORMULA PermAdmissibility-COL-01-CTLFireability-15CANNOT_COMPUTE

MC time: 0m0sec

Total processing time: 1m26sec

BK_STOP 1432725100566

--------------------

content from stderr:

check if there are places and transitions

ok

check if there are transitions without pre-places

ok

check if at least one transition is enabled in m0

ok

check if there are transitions that can never fire

ok

initing FirstDep: 0m0sec

394 637 707 902 975 1083 1152 1230 1301 1405 1460 1492 1524 1543 1632 1642 1668 1702 1775 1814 1844 1945 2017 2048 2080 2140 2226 2245 2270 2297 2381 2391 2408 2433 2489 2509 2521 2548 2590 2606 2619 2646 2689 2703 2712 2729 2779 2784 2793 2808 2844 2846 2860 2873 2921 2925 2940 2953 3001 3004 3015 3021 3065 3065 3073 3084 3297 3516 3859 4011 4176 4283 4387 4648 4756 4876 4915 5081 5139 5170 5358 5448 5579 5601 5654 5662 5818 5866 5895 6037 6088 6151 6194 6240 6242 6363 6377 6381 6455 6502 6610 6650 6709 6736 6773 6819 6870 6885 6888 6893 6901 6906 6915 6905 7007 7055 7137 7160 7239 7280 7372 7414 7484 7517 7603 7592 7626 7615 7648 7633 7623 7654 7639 7647 7625 7718 7767 7843 7856 7918 7942 8033 8072 8143 8169 8225 8238 8253 8266 8259 8277 8264 8253 8246 8222 8210 8250 8234 8308 8353 8394 8415 8479 8518 8549 8618 8664 8720 8753 8783 8786 8810 8823 8856 8818 8844 8807 8800 8778 8763 8745 8733 8712 8683 8655 8619 9436 9646 9986 10101 10489 10716 10293 10905 11284 11427 10989 11335 11706 11931 11507 11658 12055 12269 12324 12033 11625 12066 12235 12344 12502 12596 13024 13206 13348 13587 13723 13796 13997 14168 14290 14343 14570 14743 14836 14864 15146 15251 15397 15538 15638 15695 15928 16048 16258 16367 16445 16599 16670 16772 16822 16861 17003 17070 17237 17292 17394 17506 17609 17690 17735 17819 17939 18091 18196 18244 18422 18551 18627 18671 18799 18916 18971 19087 19154 19219 19245 19319 19334 19408 19437 19582 19628 19676 19769 19837 19912 19918 19939 20012 20076 20136 20255 20280 20330 20372 20399 20397 20469 20611 20667 20730 20777 20821 20864 20940 20969 21079 21172 21299 21350 21434 21530 21628 21716 21804 21843 21899 21997 22087 22113 22175 22237 22285 22292 22351 22491 22539 22623 22690 22797 22858 22883 22951 23060 23101 23172 23288 23351 23439 23503 23619 23656 23712 23761 23838 23886 23958 24106 24156 24175 24204 24311 24368 24395 24390 24411 24446 24517 24627 24710 24792 24846 24920 24955 25043 25090 25140 25209 25274 25331 25360 25380 25424 25451 25461 25478 25503 25630 25661 25720 25802 25858 25915 25921 25970 26042 26075 26105 26222 26256 26329 26397 26472 26514 26533 26610 26655 26725 26770 26893 26938 26944 26986 27060 27115 27125 27122 27137 27185 27214 27332 27367 27406 27454 27465 27487 27513 27600 27661 27739 27788 27788 27832 27891 27945 27993 28016 28007 28025 28141 28188 28189 28235 28282 28304 28293 28349 28424 28462 28526 28539 28567 28618 28640 28683 28710 28724 28772 28818 28880 28930 28931 28977 29021 29065 29097 29115 29109 29189 29261 29284 29304 29317 29344 29391 29408 29413 29425 29427 29483 29509 29521 29525 29551 29557 29565 29562 29648 29695 29735 29768 29782 29814 29832 29832 32734 33256 34054 35969 36201 37411 37902 38168 38635 39174 39204 39776 39968 40017 41305 41641 42044 42298 42562 42747 43031 43059 44759 46682 47848 49079 50407 50684 51279 51618 51941 52575 52883 53099 53278 53427 53668 53912 54037 54302 54405 54551 54643 54725 54783 54867 54911 54981

iterations count:524507 (512), effective:2412 (2)

initing FirstDep: 0m0sec

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

./auxi/order.icc:106: Exception: getting unordered element

Sequence of Actions to be Executed by the VM

This is useful if one wants to reexecute the tool in the VM from the submitted image disk.

set -x

# this is for BenchKit: configuration of major elements for the test

export BK_INPUT="PermAdmissibility-COL-01"

export BK_EXAMINATION="CTLFireability"

export BK_TOOL="marcie"

export BK_RESULT_DIR="/user/u8/hulinhub/BK_RESULTS/OUTPUTS"

export BK_TIME_CONFINEMENT="3600"

export BK_MEMORY_CONFINEMENT="16384"

# this is specific to your benchmark or test

export BIN_DIR="$HOME/BenchKit/bin"

# remove the execution directoty if it exists (to avoid increse of .vmdk images)

if [ -d execution ] ; then

rm -rf execution

fi

tar xzf /home/mcc/BenchKit/INPUTS/PermAdmissibility-COL-01.tgz

mv PermAdmissibility-COL-01 execution

# this is for BenchKit: explicit launching of the test

cd execution

echo "====================================================================="

echo " Generated by BenchKit 2-2265"

echo " Executing tool marcie"

echo " Input is PermAdmissibility-COL-01, examination is CTLFireability"

echo " Time confinement is $BK_TIME_CONFINEMENT seconds"

echo " Memory confinement is 16384 MBytes"

echo " Number of cores is 1"

echo " Run identifier is r064kn-blw3-143254880300081"

echo "====================================================================="

echo

echo "--------------------"

echo "content from stdout:"

echo

echo "=== Data for post analysis generated by BenchKit (invocation template)"

echo

if [ "CTLFireability" = "ReachabilityComputeBounds" ] ; then

echo "The expected result is a vector of positive values"

echo NUM_VECTOR

elif [ "CTLFireability" != "StateSpace" ] ; then

echo "The expected result is a vector of booleans"

echo BOOL_VECTOR

else

echo "no data necessary for post analysis"

fi

echo

if [ -f "CTLFireability.txt" ] ; then

echo "here is the order used to build the result vector(from text file)"

for x in $(grep Property CTLFireability.txt | cut -d ' ' -f 2 | sort -u) ; do

echo "FORMULA_NAME $x"

done

elif [ -f "CTLFireability.xml" ] ; then # for cunf (txt files deleted;-)

echo echo "here is the order used to build the result vector(from xml file)"

for x in $(grep '

echo "FORMULA_NAME $x"

done

fi

echo

echo "=== Now, execution of the tool begins"

echo

echo -n "BK_START "

date -u +%s%3N

echo

timeout -s 9 $BK_TIME_CONFINEMENT bash -c "/home/mcc/BenchKit/BenchKit_head.sh 2> STDERR ; echo ; echo -n \"BK_STOP \" ; date -u +%s%3N"

if [ $? -eq 137 ] ; then

echo

echo "BK_TIME_CONFINEMENT_REACHED"

fi

echo

echo "--------------------"

echo "content from stderr:"

echo

cat STDERR ;